| Skip Navigation Links | |

| Exit Print View | |

|

Writing Device Drivers Oracle Solaris 11 Express 11/10 |

| Skip Navigation Links | |

| Exit Print View | |

|

Writing Device Drivers Oracle Solaris 11 Express 11/10 |

Part I Designing Device Drivers for the Oracle Solaris Platform

1. Overview of Oracle Solaris Device Drivers

2. Oracle Solaris Kernel and Device Tree

5. Managing Events and Queueing Tasks

7. Device Access: Programmed I/O

10. Mapping Device and Kernel Memory

13. Hardening Oracle Solaris Drivers

14. Layered Driver Interface (LDI)

Part II Designing Specific Kinds of Device Drivers

15. Drivers for Character Devices

18. SCSI Host Bus Adapter Drivers

19. Drivers for Network Devices

Part III Building a Device Driver

21. Compiling, Loading, Packaging, and Testing Drivers

22. Debugging, Testing, and Tuning Device Drivers

23. Recommended Coding Practices

Member Alignment in SPARC Structures

SPARC Multiply and Divide Instructions

PCI Configuration Address Space

PCI Configuration Base Address Registers

PCI Hardware Configuration Files

SBus Hardware Configuration Files

B. Summary of Oracle Solaris DDI/DKI Services

C. Making a Device Driver 64-Bit Ready

Data types have no alignment restrictions. However, extra memory cycles might be required for the x86 processor to properly handle misaligned data transfers.

Note - Drivers should not perform floating-point operations, as these operations are not supported in the kernel.

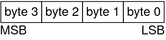

The x86 processors use little-endian byte ordering. The least significant byte (LSB) of an integer is stored at the lowest address of the integer. The most significant byte is stored at the highest address for data items in this processor. For example, byte 7 is the most significant byte for 64-bit processors.

Both Intel Corporation and AMD publish a number of books on the x86 family of processors. See http://www.intel.com and http://www.amd.com/.