# Netra<sup>™</sup> CP2500 Board Installation and Technical Reference Manual

Sun Microsystems, Inc. www.sun.com

Part No. 819-1747-11 March 2007, Revision A

Submit comments about this document at: <a href="http://www.sun.com/hwdocs/feedback">http://www.sun.com/hwdocs/feedback</a>

Copyright 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, AnswerBook2, docs.sun.com, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and in other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc

PICMG and the PICMG logo are registered trademarks of the PCI Industrial Computers Manufacturers Group.

The OPEN LOOK and Sun™ Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

U.S. Government Rights—Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, Californie 95054, États-Unis. Tous droits réservés.

Sun Microsystems, Inc. possède les droits de propriété intellectuels relatifs à la technologie décrite dans ce document. En particulier, et sans limitation, ces droits de propriété intellectuels peuvent inclure un ou plusieurs des brevets américains listés sur le site http://www.sun.com/patents, un ou les plusieurs brevets supplémentaires ainsi que les demandes de brevet en attente aux les États-Unis et dans d'autres pays.

Ce document et le produit auquel il se rapporte sont protégés par un copyright et distribués sous licences, celles-ci en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a.

Tout logiciel tiers, sa technologie relative aux polices de caractères, comprise, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit peuvent dériver des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux États-Unis et dans d'autres pays, licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, Java, AnswerBook2, docs.sun.com, et Solaris sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux États-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux États-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

PICMG, le logo PICMG, sont des marques de fabrique ou des marques déposées de PCI Industrial Computers Manufacturers Group.

L'interface utilisateur graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox dans la recherche et le développement du concept des interfaces utilisateur visuelles ou graphiques pour l'industrie informatique. Sun détient une license non exclusive de Xerox sur l'interface utilisateur graphique Xerox, cette licence couvrant également les licenciés de Sun implémentant les interfaces utilisateur graphiques OPEN LOOK et se conforment en outre aux licences écrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ÉTAT" ET TOUTES AUTRES CONDITIONS, DÉCLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES DANS LA LIMITE DE LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE À LA QUALITÉ MARCHANDE, À L'APTITUDE À UNE UTILISATION PARTICULIÈRE OU À L'ABSENCE DE CONTREFAÇON.

## Contents

### Preface xiii

| 1. | Netra  | CP2500   | Board Overview 1–1                       |

|----|--------|----------|------------------------------------------|

|    | 1.1    | Netra (  | CP2500 Board Features 1–2                |

|    | 1.2    | Netra (  | CP2500 Board System Configurations 1-5   |

|    |        | 1.2.1    | PMC Modules 1–7                          |

|    |        | 1.2.2    | Rear Transition Modules 1–8              |

|    | 1.3    | Hot-Sw   | vap Support 1–12                         |

|    | 1.4    | System   | Requirements 1–13                        |

|    |        | 1.4.1    | Hardware Requirements 1–13               |

|    |        | 1.4.2    | Software Requirements 1–14               |

|    | 1.5    | Physica  | al Description 1–15                      |

|    |        | 1.5.1    | Front Panel Components 1–17              |

|    |        | 1.5.2    | Functional Block Diagram 1–19            |

|    | 1.6    | Contac   | ting Technical Support 1–20              |

|    |        | 1.6.1    | Board Identification 1–20                |

| 2. | Instal | ling the | Netra CP2500 Board in a cPSB Chassis 2–1 |

- 2.1 Installation Options 2–2

- 2.2 Equipment and Operator Safety 2–3

- 2.3 Materials and Tools Required 2–4

- 2.4 Preparing for the Installation 2–4

- 2.4.1 Checking Power, Thermal, Environmental, and Space Requirements 2–5

- 2.4.2 Determining Local Network IP Addresses and Hostnames 2–5

- 2.4.3 Installation Procedure Summary 2–6

- 2.5 Configuring the Board Hardware 2–7

- 2.5.1 Installing an Optional PMC Device 2–7

- 2.5.2 Setting the SW3301 DIP Switch 2–11

- 2.5.3 Replacing the SEEPROM 2–13

- 2.5.4 Preparing the RTM-S for Installation 2–15

- 2.5.4.1 Differences Between Available Netra CP2500 Rear Transition Modules 2–15

- 2.5.4.2 Setting RTM-S DIP Switches 2–15

- 2.6 Installing Boards Into a cPSB Chassis 2–19

- 2.6.1 Installing the RTM-S 2–19

- 2.6.2 Installing the Netra CP2500 Board 2–20

- 2.7 Setting Up an Assembled Netra CP2500 Board 2–22

- 2.8 Initial Power On and Firmware Upgrade 2–23

- 2.8.1 Powering On the System 2–23

- 2.8.2 Booting From a PMC Disk 2–24

- 2.8.3 Determining Firmware Versions 2–24

- 2.8.3.1 Determining Firmware Versions From OpenBoot PROM Prompt 2–24

- 2.8.3.2 Determining Firmware Versions From the Solaris Prompt 2–25

- 2.8.4 Upgrading the OpenBoot PROM and SMC Firmware 2–26

#### 3. Configuring Netra CP2500 Board Software 3–1

3.1 Hot-Swap Information 3–2

- 3.1.1 Hot-Swapping the Netra CP2500 Board 3–23.1.1.1 Hot-Swap Status LED 3–3

- 3.1.2 Retrieving Device Information 3–5

- 3.2 Setting the Time of Day 3–8

- 3.3 Downloading and Installing SunVTS 3–9

### 4. Configuring and Using the Netra CP2500 Board Firmware 4–1

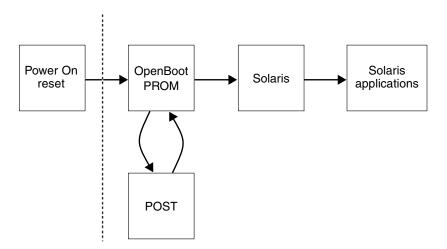

- 4.1 Firmware Initialization 4–2

- 4.1.1 OpenBoot PROM Operation 4–3

- 4.2 Firmware Configuration Variables 4–6

- 4.2.1 OpenBoot PROM Configuration Variables 4–6

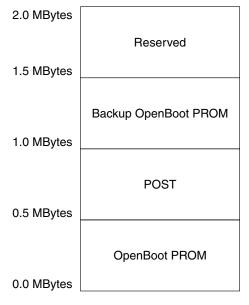

- 4.3 System Flash PROM Memory Map 4–9

- 4.4 Environmental Monitoring Support at OpenBoot PROM 4–10

- 4.4.1 CPU Thermal Sensor 4–10

- 4.4.2 Reading the CPU Temperature Limits 4–11

- 4.5 System Management Controller (SMC) Firmware 4–13

- 4.5.1 SMC Configuration Block 4–13

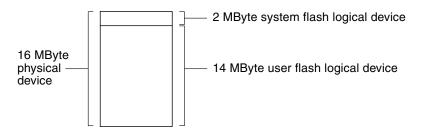

- 4.6 Using the Flash PROMs 4–15

- 4.7 Booting the Board Using the Backup OpenBoot PROM 4–15

- 4.7.1 Updating the OpenBoot PROM and SMC Firmware 4–17

- 4.8 Firmware Diagnostics 4–18

- 4.8.1 Setting Diagnostic Levels 4–18

- 4.8.2 OpenBoot PROM On-Board Diagnostics 4–18

- 4.8.3 OpenBoot Diagnostics 4–19

### 5. Removing and Replacing Board Hardware 5–1

- 5.1 Field Replaceable Units 5–1

- 5.2 Handling Equipment and Assembling Tools 5–2

- 5.3 Displaying the Solaris FRU ID 5–2

- 5.4 Removing and Replacing the Board From the Chassis 5–4

- 5.4.1 Removing the Board From the Chassis 5–4

- 5.4.2 Replacing the Board in the System 5–8

- 5.5 Removing and Replacing the SEEPROM 5–9

- 5.5.1 Removing the SEEPROM 5–9

- 5.5.2 Replacing the SEEPROM 5–10

- 5.6 Removing and Replacing a PMC Device 5–11

- 5.6.1 Removing a PMC Device 5–11

- 5.6.2 Replacing a PMC Device 5–13

- 5.7 Removing and Replacing Memory Modules 5–14

- 5.7.1 Removing DIMM Memory Modules 5–15

- 5.7.2 Installing Memory Modules 5–17

#### A. Specifications A–1

- A.1 System Compatibility Specifications A–2

- A.2 CPU Specifications A-2

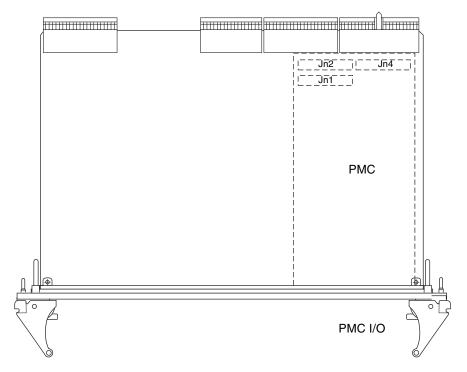

- A.3 PMC Interface Specifications A–3

- A.4 Power Requirements A–3

- A.5 Mechanical Specifications A–4

- A.6 Environmental Specifications A–6

- A.7 Cooling Requirements A-6

- A.8 Reliability and Availability Specifications A–6

#### B. Connectors, Pinouts, and Switch Settings B–1

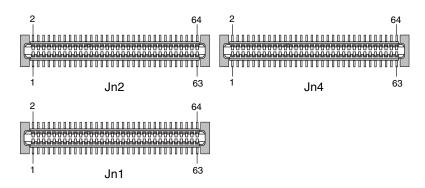

- B.1 PMC Connector B–2

- B.1.1 PMC Connector Interfaces B–3

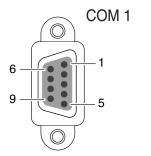

- B.2 Front Panel Serial Connector B–8

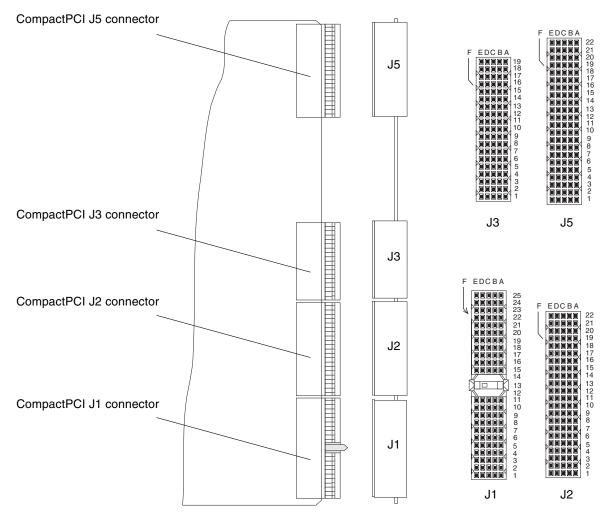

- B.3 Backplane Connectors B–9

- B.3.1 CompactPCI J1/P1 Connector Pinouts B–10

- B.3.2 CompactPCI J1/P1 Signal Descriptions B-11

- B.3.3 CompactPCI J2/P2 Connector Pinouts B–13

- B.3.4 CompactPCI J2/P2 Signal Descriptions B-14

- B.3.5 CompactPCI J3/P3 Connector Pinouts B–15

- B.3.6 CompactPCI J3/P3 Signal Descriptions B-15

- B.3.7 CompactPCI J5/P5 Connector Pinouts B–16

- B.3.8 CompactPCI J5/P5 Signal Descriptions B-17

- B.4 DIP Switch Settings B–18

# Figures

| FIGURE 1-1  | Typical Netra CP2500 Board 1-2                                          |

|-------------|-------------------------------------------------------------------------|

| FIGURE 1-2  | Netra CP2500 Boards Installed in Netra CT 410 and 810 Servers 1-5       |

| FIGURE 1-3  | Netra CP2500 Board Diskless Client Configuration Example 1-6            |

| FIGURE 1-4  | Netra CP2500 Node Board Mounting Configuration Example 1-7              |

| FIGURE 1-5  | Netra CP2500 RTM-H for Netra CT Server Host Slots 1–9                   |

| FIGURE 1-6  | Netra CP2500 RTM-S for Netra CT Satellite Slots and cPSB Node Slots 1–9 |

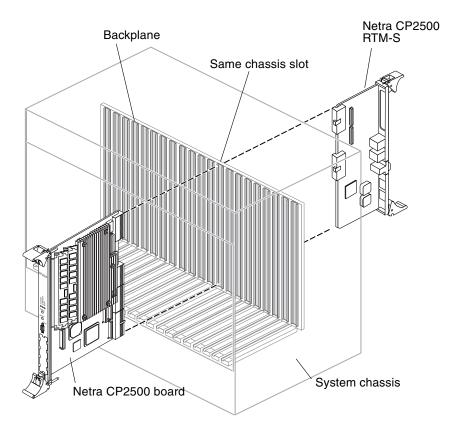

| FIGURE 1-7  | Netra CP2500 Board and a RTM-S in a Typical cPSB Chassis 1–10           |

| FIGURE 1-8  | Netra CP2500 Board Layout 1-15                                          |

| FIGURE 1-9  | Typical Netra CP2500 Board – Solder Side 1–16                           |

| FIGURE 1-10 | Netra CP2500 Board Front Panel 1-17                                     |

| FIGURE 1-11 | Netra CP2500 Board Functional Block Diagram 1–19                        |

| FIGURE 1-12 | Typical Netra CP2500 Board Barcode Labeling 1-21                        |

| FIGURE 2-1  | PMC Slot Location 2–7                                                   |

| FIGURE 2-2  | Removing the PMC Filler Panel 2–9                                       |

| FIGURE 2-3  | Inserting the PMC Into the PMC Slot 2–9                                 |

| FIGURE 2-4  | Pressing the PMC Into the PMC Connectors – Side View 2–10               |

| FIGURE 2-5  | Securing the PMC Screws 2–10                                            |

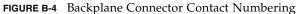

| FIGURE 2-6  | Setting the SW3301 Switch 2 to cPSB Chassis Operation 2–12              |

| FIGURE 2-7  | Replacing the SEEPROM 2-14                                              |

| FIGURE 2-8  | S1301 DIP Switch Bank Location on the RTM-S 2-16                        |

- FIGURE 2-9 Setting the S1301 DIP Switches for cPSB Networks 2–17

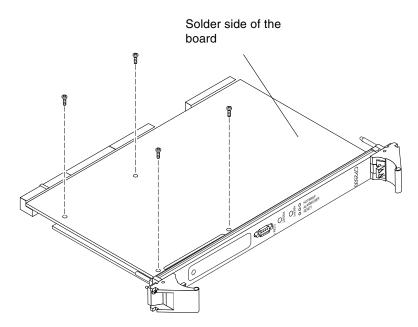

- FIGURE 2-10 S1302 DIP Switch Bank Location on the Solder Side of the RTM-S 2–18

- FIGURE 2-11 Setting the S1302 DIP Switches for cPSB Networks 2–18

- FIGURE 2-12 Installing the Netra CP2500 Board and RTM-S in an cPSB Chassis 2–20

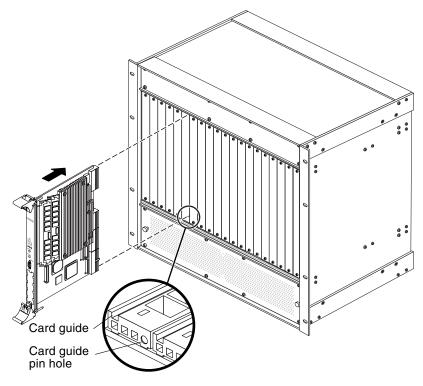

- FIGURE 2-13 Installing a Netra CP2500 Board Into a cPSB Chassis Slot 2–21

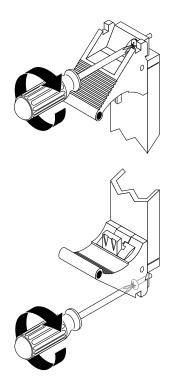

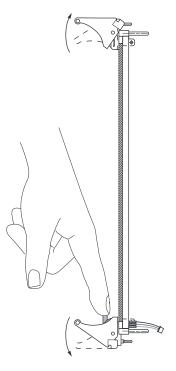

- FIGURE 2-14 Securing the Board in the Chassis Slot 2–22

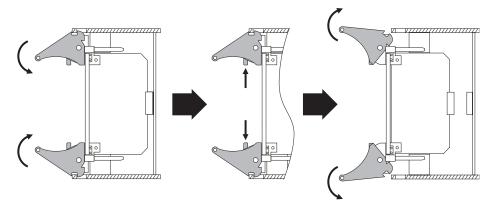

- FIGURE 3-1 Releasing the Netra CP2500 Ejector Levers 3–3

- FIGURE 3-2 Blue Hot-Swap LED Location 3–4

- FIGURE 4-1 Control Flow From Power On for Firmware 4–2

- FIGURE 4-2 System Flash PROM Map 4–9

- FIGURE 4-3 System Flash and User Flash Logical Devices on Same Physical Device 4–15

- FIGURE 4-4 Setting Switch 1 on the SW3301 DIP Switch Bank to Closed 4–16

- FIGURE 5-1 Loosening the Ejector Lever Captive Screws 5–5

- FIGURE 5-2 Releasing the Netra CP2500 Ejector Levers 5–6

- FIGURE 5-3 Blue Hot-Swap LED Location 5–7

- FIGURE 5-4 Unlocking and Using the Ejector Levers to Remove the Board 5–8

- FIGURE 5-5 Removing the SEEPROM 5–10

- FIGURE 5-6 Loosening the PMC Device Screws 5–12

- FIGURE 5-7 Lifting the PMC Device From the Board PMC Connectors 5–12

- FIGURE 5-8 Replacing the PMC Filler Panel 5–13

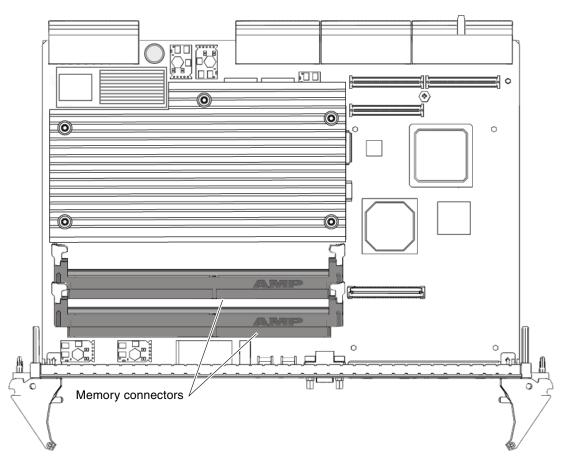

- FIGURE 5-9 Location of Memory Connectors 5–15

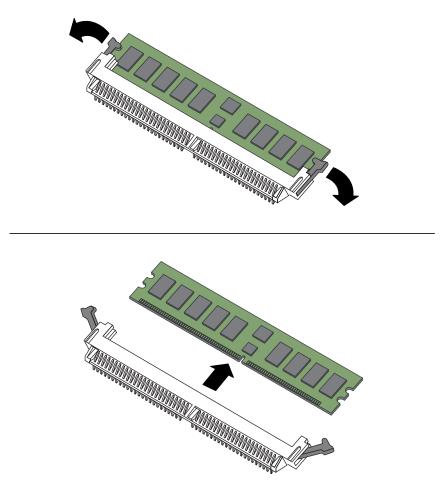

- FIGURE 5-10 Removing a DIMM 5–17

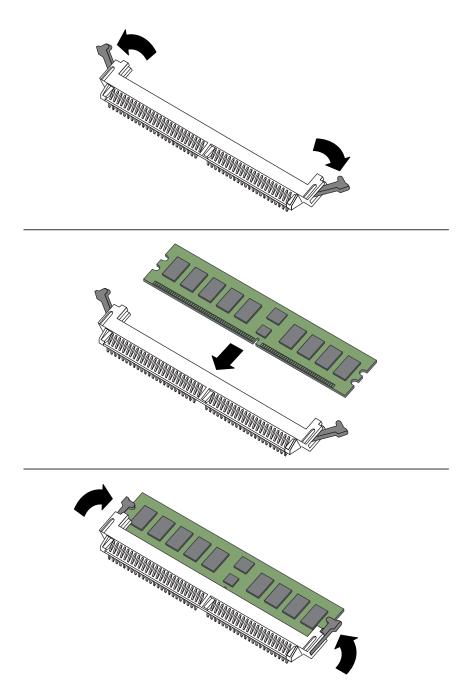

- FIGURE 5-11 Installing a DIMM Into a Board Memory Connector 5–19

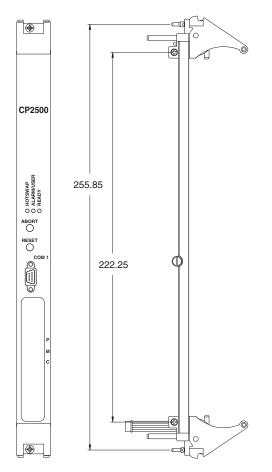

- FIGURE A-1 Physical Dimensions of the Netra CP2500 Front Panel A-4

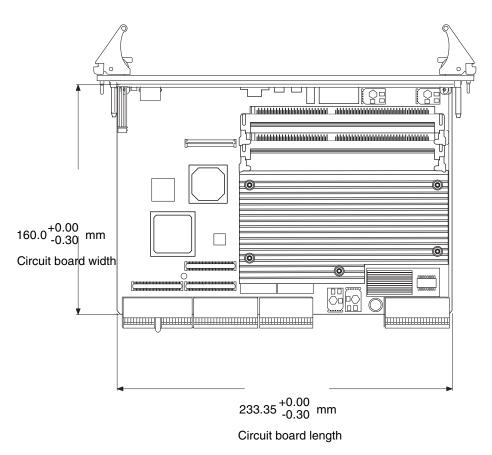

- FIGURE A-2 Mechanical Dimensions of the Netra CP2500 Board A–5

- FIGURE B-1 Netra CP2500 Board PMC Port Connectors B-2

- FIGURE B-2 PMC Connector Slot Connector Pins B–3

- FIGURE B-3 Front Panel Serial Port Diagram B–8

- FIGURE B-4 Backplane Connector Contact Numbering B–9

- FIGURE B-5 SW3301 DIP Switch Location B–18

## Tables

| TABLE 1-1 | Feature Summary 1–3                                                         |

|-----------|-----------------------------------------------------------------------------|

| TABLE 1-2 | Netra CP2500 Board Role Examples 1–6                                        |

| TABLE 1-3 | Netra CP2500 Board I/O Configurations 1-11                                  |

| TABLE 1-4 | Netra CP2500 Board Hot-Swap Support 1-12                                    |

| TABLE 1-5 | cPSB System and Other Minimum Requirements 1–14                             |

| TABLE 1-6 | Front Panel I/O 1-18                                                        |

| TABLE 2-1 | Hardware Installation Options 2–2                                           |

| TABLE 2-2 | Your Local Network Information 2–5                                          |

| TABLE 3-1 | PICL FRU Tree Entries and Description for the Netra CP2500 Board 3-8        |

| TABLE 4-1 | OpenBoot PROM NVRAM Configuration Variables 4–6                             |

| TABLE 4-2 | Description of Values Displayed by Solaris Commands 4–12                    |

| TABLE 5-1 | Description of Fields in Typical prtfru Command Display Output 5-3          |

| TABLE A-1 | CPU Specifications A-2                                                      |

| TABLE A-2 | PMC Interface Specification A-3                                             |

| TABLE A-3 | Netra CP2500 Backplane Connector Power Requirements by Connection Phase A-3 |

| TABLE A-4 | Environmental Conditions and Limits A-6                                     |

| TABLE B-1 | PMC Jn1 Connector Interface B–3                                             |

| TABLE B-2 | PMC Jn2 Connector Interface B–5                                             |

| TABLE B-3 | PMC Jn4 Connector Interface B–6                                             |

| TABLE B-4 | Serial Micro DB9 Connector Pinouts B-8                                      |

- TABLE B-5 CompactPCI J2/P2 Connector Pin Assignments B–10

- TABLE B-6

CompactPCI J1/P1 Signal Descriptions

B-11

- TABLE B-7

CompactPCI J2/P2 Connector Pin Assignments

B–13

- TABLE B-8

CompactPCI J2/P2 Signal Descriptions

B-14

- TABLE B-9 CompactPCI J3/P3 Connector Pin Assignments B–15

- TABLE B-10

CompactPCI J3/P3 Signal Descriptions

B–15

- TABLE B-11

CompactPCI J5/P5 Connector Pin Assignments

B–16

- TABLE B-12 Serial COM Port and RS232 Level CompactPCI J5/P5 Signal Descriptions B-17

- TABLE B-13 Miscellaneous CompactPCI J5/P5 Signal Descriptions B–17

- TABLE B-14 SW3301 Switch Descriptions B-19

## Preface

The Netra CP2500 Board Installation and Technical Reference Manual describes how to install and configure the Netra<sup>™</sup> CP2500 board. This document is written for system integration engineers, field application engineers, service engineers, and other professionals involved in the integration of these boards into systems.

## How This Document Is Organized

Chapter 1 presents an overview of the Netra CP2500 board.

Chapter 2 provides the hardware configuration and installation tasks.

Chapter 3 provides instructions on the software configuration.

Chapter 4 gives information on the firmware.

Chapter 5 contains hardware service procedures.

Appendix A lists the board specifications.

Appendix B defines the board connector pinouts.

# Using UNIX Commands

This document might not contain information about basic UNIX<sup>®</sup> commands and procedures such as shutting down the system, booting the system, and configuring devices. Refer to the following for this information:

- Software documentation that you received with your system

- Solaris<sup>TM</sup> Operating System documentation, which is at:

http://docs.sun.com

## Shell Prompts

| Shell                                 | Prompt        |  |

|---------------------------------------|---------------|--|

| C shell                               | machine-name% |  |

| C shell superuser                     | machine-name# |  |

| Bourne shell and Korn shell           | \$            |  |

| Bourne shell and Korn shell superuser | #             |  |

# **Typographic Conventions**

| Typeface* | Meaning                                                                                                                     | Examples                                                                                                      |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| AaBbCc123 | The names of commands, files,<br>and directories; on-screen<br>computer output                                              | Edit your.login file.<br>Use ls -a to list all files.<br>% You have mail.                                     |  |

| AaBbCc123 | What you type, when contrasted with on-screen computer output                                                               | % <b>su</b><br>Password:                                                                                      |  |

| AaBbCc123 | Book titles, new words or terms,<br>words to be emphasized.<br>Replace command-line variables<br>with real names or values. | hasized. These are called <i>class</i> options.<br>Id-line variables You <i>must</i> be superuser to do this. |  |

\* The settings on your browser might differ from these settings.

## **Related Documentation**

The documents listed as online are available at:

http://www.sun.com/documentation

| Application                                             | Title                                                                              | Part Number | Format      | Location     |

|---------------------------------------------------------|------------------------------------------------------------------------------------|-------------|-------------|--------------|

| Board installation<br>and reference                     | Netra CP2500 Board Installation and Technical<br>Reference Manual                  | 819-1747    | PDF<br>HTML | Online       |

| Board news and updates                                  | Netra CP2500 Board Release Notes                                                   | 819-1748    | PDF<br>HTML | Online       |

| Programming                                             | Netra CP2500 Board Programming Guide                                               | 819-1749    | PDF<br>HTML | Online       |

| Safety information                                      | Important Safety Information for Sun Hardware<br>Systems                           | 816-7190    | Printed     | Shipping kit |

| Safety and compliance                                   | Netra CP2500 Board Safety and Compliance<br>Manual                                 | 819-1750    | PDF<br>HTML | Online       |

| Rear transition<br>module installation<br>and reference | Netra CP2500 Rear Transition Module<br>Installation and Technical Reference Manual | 819-1753    | PDF<br>HTML | Online       |

# Documentation, Support, and Training

| Sun Function  | URL                               |  |  |  |

|---------------|-----------------------------------|--|--|--|

| Documentation | http://www.sun.com/documentation/ |  |  |  |

| Support       | http://www.sun.com/support/       |  |  |  |

| Training      | http://www.sun.com/training/      |  |  |  |

## Third-Party Web Sites

Sun is not responsible for the availability of third-party web sites mentioned in this document. Sun does not endorse and is not responsible or liable for any content, advertising, products, or other materials that are available on or through such sites or resources. Sun will not be responsible or liable for any actual or alleged damage or loss caused by or in connection with the use of or reliance on any such content, goods, or services that are available on or through such sites or resources.

You can obtain more information about PCI specifications at the PCI Industrial Computer Manufacturer Group (PICMG®) web site:

http://www.picmg.org/

## Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can submit your comments by going to:

http://www.sun.com/hwdocs/feedback

Please include the title and part number of your document with your feedback:

Netra CP2500 Board Installation and Technical Reference Manual, part number 819-1747-11

## Netra CP2500 Board Overview

The Netra CP2500 board is a crucial building block that network equipment providers (NEPs) and carriers can use when scaling and improving the availability of carrier-grade systems. Based on industry standards, the Netra CP2500 board provides high performance and is powered by a UltraSPARC® IIIi processor. The board enables you to add a third-party PCI mezzanine card (PMC) to tailor solutions to your specific application needs.

When replacing the Netra CP2140 host and Netra CP2160 satellite CompactPCI (cPCI) boards in the Netra CT 410 and 810 servers, the Netra CP2500 board provides a sizeable increase in Netra CT server performance.

The Netra CP2500 board provides PCI Industrial Computers Manufacturers' Group (PICMG) CompactPCI Packet Switched Backplane (cPSB) compliance. To meet the requirements of the communications and service provider environments, the board is NEBS Level 3 compliant, and the Netra CT 410 and 810 servers remain NEBS Level 3 certified with the Netra CP2500 board installed.

This chapter contains the following sections:

- Section 1.1, "Netra CP2500 Board Features" on page 1-2

- Section 1.2, "Netra CP2500 Board System Configurations" on page 1-5

- Section 1.3, "Hot-Swap Support" on page 1-12

- Section 1.4, "System Requirements" on page 1-13

- Section 1.6, "Contacting Technical Support" on page 1-20

## 1.1 Netra CP2500 Board Features

The Netra CP2500 board is a single-board computer designed for high-performance, embedded, compute density applications. The Netra CP2500 board has system management controller (SMC) capability that supports hot-swap operations, system management, and environmental monitoring. Powered by a UltraSPARC IIIi processor and including on-board I/O and one PMC slot, the Netra CP2500 board is an ideal platform for NEPs to use for a wide variety of Solaris Operating System applications.

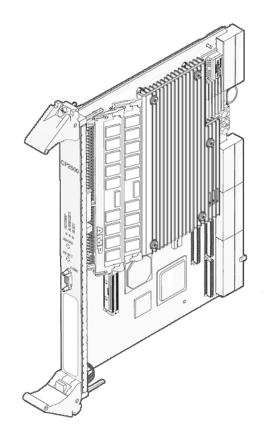

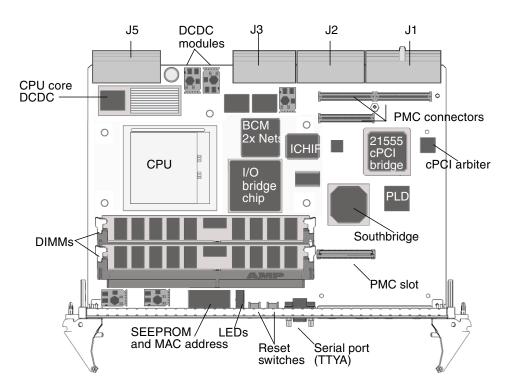

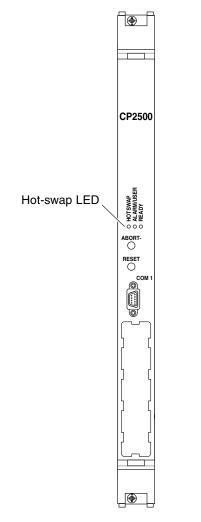

FIGURE 1-1 displays an illustration of a typical Netra CP2500 board, and TABLE 1-1 lists a summary of the board features.

FIGURE 1-1 Typical Netra CP2500 Board

### TABLE 1-1 Feature Summary

| Feature                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                            | UltraSPARC IIIi processor with 1 Mbyte L2 cache                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Memory                         | Two 184-pin memory slots available for Sun-supplied, 0.72-inch DDR-1 very low-profile (VLP) DIMMs. Total memory capacity is 2 Gbytes using two 1 Gbyte DIMMs.                                                                                                                                                                                                                                                                                                               |

| Power<br>requirement           | Estimated at 55 W (typical) and 65 W (peak maximum) with a RTM and two 1.0 GByte DIMMs installed.<br>(The power requirements exclude PMC power.)                                                                                                                                                                                                                                                                                                                            |

| PICMG and PCI<br>compatibility | <ul> <li>PICMG 2.0 R3.0 CompactPCI bus specification for 33 MHz PCI speed</li> <li>PICMG 2.1 R2.0 Hot-Swap Specification*</li> <li>PICMG 2.10 R1.0 Keying of cPCI boards and backplanes</li> <li>PICMG 2.16 R1.0 CompactPCI packet switching backplane</li> <li>PICMG 2.3 R1.0 PMC on CompactPCI Tables 1 and 3</li> <li>PICMG 2.9 R1.0 System Management Specification</li> <li>PMC Specification P1386 Draft 2.4</li> <li>CMC P1386 Draft 2.4 Standard for CMC</li> </ul> |

| cPSB node<br>board support     | The board functions as a cPSB node board in a cPSB chassis with the appropriate Solaris Operating System software installed.                                                                                                                                                                                                                                                                                                                                                |

| cPCI host-mode<br>support      | The board functions as a system host board when installed in the host<br>slot of a Netra CT 410 or 810 server with the appropriate Solaris<br>Operating System software installed                                                                                                                                                                                                                                                                                           |

| cPCI satellite<br>mode support | The board functions as a satellite board when installed in Netra CT 410 or 810 server with the appropriate Solaris Operating System software installed.                                                                                                                                                                                                                                                                                                                     |

| IPMI system<br>management      | Uses IPMI communications with Baseboard Management Controller (BMC); performs environmental monitoring on local board interface for example temperature sense, FRU ID, and control.                                                                                                                                                                                                                                                                                         |

| Hot-swap<br>support            | Basic and full hot-swap support. High-availability (HA) hot-swap support when used as a cPSB node board, Netra CT 410 or 810 satellite or host cPCI board.                                                                                                                                                                                                                                                                                                                  |

| Operating system               | Solaris 9 Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Front I/O and connectors       | <ul><li>One PMC slot</li><li>One serial port (can only be used if rear serial port COM A is not used)</li></ul>                                                                                                                                                                                                                                                                                                                                                             |

| TABLE 1-1Feature Su | mmary (Continued) |

|---------------------|-------------------|

|---------------------|-------------------|

| Feature                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rear transition<br>modules (RTM)<br>connectors<br>(optional)<br>RTM-H | <ul> <li>CompactPCI rear transition module host card (referred to in this document as RTM-H). The RTM-H is only supported in Netra CT 410 and 810 servers, and contains the following features:</li> <li>Four 10/100 Ethernet ports</li> <li>Two serial ports (One is mutually exclusive with the front panel serial connector)</li> </ul>                                                                                                                                                              |

|                                                                       | <ul> <li>Two internal SCSI connectors on the J4 and J5 connectors provided by<br/>the dual PCI to SCSI controller in a Netra CT 410 or 810 server (not<br/>accessible from the rear panel)</li> </ul>                                                                                                                                                                                                                                                                                                   |

| RTM-S                                                                 | <ul> <li>CompactPCI rear transition module satellite card (referred to in this document as RTM-S). While in cPCI mode, the RTM-S is supported in Netra CT 410 and 810 servers only. However, you can set mechanical DIP switches on the Netra CP2500 board and the RTM-S card to enable the Netra CP2500 board to be used as a node board in a cPSB chassis:</li> <li>Four 10/100 Ethernet ports</li> <li>Two serial ports (one is mutually exclusive with the front panel serial connector)</li> </ul> |

| PMC I/O                                                               | Provision for adding one independent hardware vendor (IHV) supplied PMC expansion ports on front panel.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Watchdog timer                                                        | Two-level watchdog timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NVRAM                                                                 | 8 Kbyte nonvolatile serial I <sup>2</sup> c EEPROM (SEEPROM) to save OpenBoot <sup>TM</sup> PROM configuration.                                                                                                                                                                                                                                                                                                                                                                                         |

| Flash memory                                                          | <ul><li>Single 16 Mbyte flash memory, divided into:</li><li>2 Mbyte system flash</li><li>14 Mbyte user flash</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |

| NEBS                                                                  | NEBS Level 3 compliant; Netra CT 410 and 810 servers remain NEBS Level 3 certified with installed Netra CP2500 boards installed.                                                                                                                                                                                                                                                                                                                                                                        |

| Flash update                                                          | Flash memory can be updated from downloaded files.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

\* The Netra CP2500 blue hot-swap LED is in a noncompliant location.

**Note** – Sun does not support installing a PMC interface module (PIM) device on either the RTM-S or the RTM-H.

**Note** – For EMI compliance of the front access ports, use shielded cables on all I/O ports. The shields for all shielded cables must be terminated on both ends.

## Netra CP2500 Board System Configurations

1.2

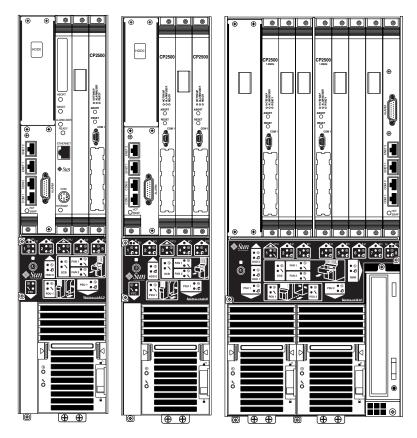

The Netra CP2500 board can be installed in the host or a satellite slot of a Netra CT 410 or 810 CompactPCI server, as shown in FIGURE 1-2 and described in TABLE 1-2. Refer to the Netra CT 410 and 810 server documentation for information about installing and using the Netra CP2500 board in a Netra CT server.

FIGURE 1-2 Netra CP2500 Boards Installed in Netra CT 410 and 810 Servers

| TABLE 1-2 | Netra | CP2500 | Board | Role | Examples |

|-----------|-------|--------|-------|------|----------|

|-----------|-------|--------|-------|------|----------|

| Callout Number | a Board and Role in Netra CT Server                              |  |  |

|----------------|------------------------------------------------------------------|--|--|

| 1              | Netra CP2140 board as a host board in a Netra CT 410 server      |  |  |

| 2              | Netra CP2500 board as a satellite board in a Netra CT 410 server |  |  |

| 3              | Netra CP2500 board as a host board in a Netra CT 410 server      |  |  |

| 4              | Netra CP2500 board as a satellite board in a Netra CT 410 server |  |  |

| 5              | Netra CP2500 board as a host board in a Netra CT 810 server      |  |  |

| 6              | Netra CP2500 board as a satellite board in a Netra CT 810 server |  |  |

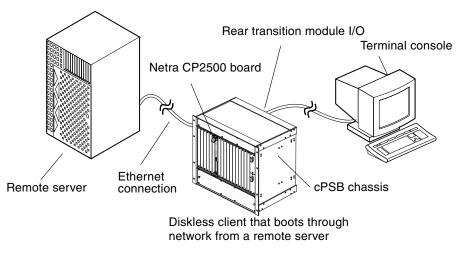

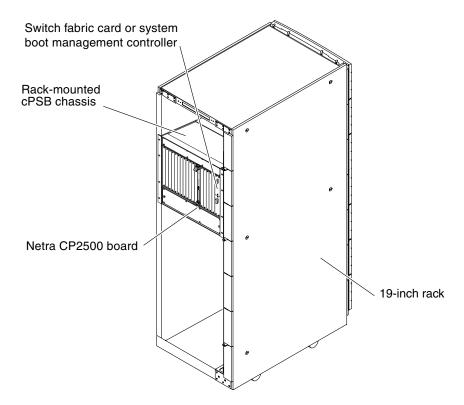

The Netra CP2500 board can also be mounted in various cPSB enclosures, such as those shown in FIGURE 1-3 and FIGURE 1-4.

You can deploy the Netra CP2500 boards in a number of cPSB configurations to suit your specific requirements. For example, the board can be configured to boot from a network as a diskless client over either a cPSB backplane network or an RTM Ethernet network connection. Alternatively, the Netra CP2500 board can be purchased with an installed PMC hard drive, which can provide local disk support I/O and may optionally be used as a boot path. The installation procedure is independent of the type of enclosure, whether a floor-mounting rack or a bench-top cabinet is used.

FIGURE 1-3 Netra CP2500 Board Diskless Client Configuration Example

FIGURE 1-4 Netra CP2500 Node Board Mounting Configuration Example

### 1.2.1 PMC Modules

While the Netra CP2500 board has only one serial port on the front panel, IHV-built PMC modules can provide additional I/O to the front panel. PMC modules decode their custom I/O from the Netra board's on-board PCI bus signals.

**Note** – Sun does not support installing a PMC interface module (PIM) device on either the RTM-S or the RTM-H.

**Note** – The Netra CP2500 board has one PMC I/O slot. If you purchase a board with a PMC disk drive, you will not be able to install an additional PMC device.

## 1.2.2 Rear Transition Modules

There are two optional transition modules (RTMs) available for the Netra CP2500 board:

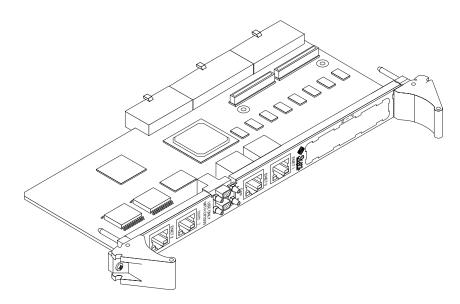

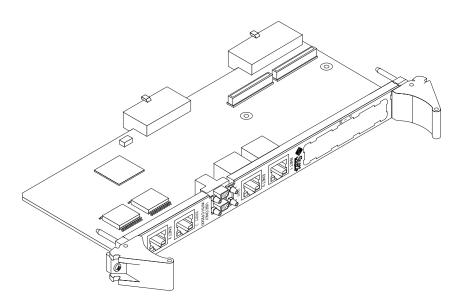

- Netra CP2500 RTM-H (FIGURE 1-5) Designed to work exclusively in the host slot of the Netra CT 410 and 810 cPCI servers (see FIGURE 1-2)

- Netra CP2500 RTM-S (FIGURE 1-6) Usable in either a satellite slot of a Netra CT 410 and 810 cPCI servers (see FIGURE 1-2) or in a node slot of a cPSB chassis (see FIGURE 1-7)

You can install the RTM-H and RTM-S into rear slots of the Netra CT server, opposite the appropriate Netra CP2500 board. These rear transition modules connect with the board's CompactPCI connectors through the Netra CT server midplane pins and carry four Ethernet ports, and two serial ports out to its rear panel. Refer to the *Netra CT Server Installation Guide* (819-2740) for installation and cabling instructions.

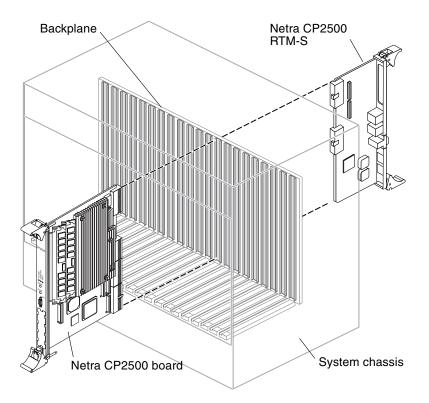

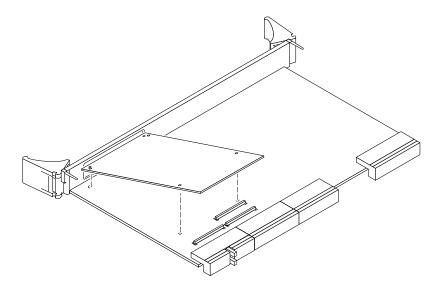

After setting a DIP switch on the Netra CP2500 board and two banks of DIP switches on the RTM-S, you can install the Netra CP2500 board and the RTM-S into a cPSB chassis (see FIGURE 1-7). See Chapter 2 for cPSB chassis installation instructions, including how to set these mechanical switches.

**Note** – For complete information about the two Netra CP2500 rear transition modules, refer to the *Netra CP2500 Rear Transition Module Installation and Technical Reference Manual* (819-1753).

FIGURE 1-5 Netra CP2500 RTM-H for Netra CT Server Host Slots

FIGURE 1-7 shows the relationship between the Netra CP2500 board, the RTM-S, and the backplane in a typical cPSB chassis.

FIGURE 1-7 Netra CP2500 Board and a RTM-S in a Typical cPSB Chassis

**Note** – To satisfy EMI compliance standards, you must use shielded cables for serial ports when using an RTM with the Netra CP2500 board. The shields for all shielded cables must be terminated on both ends. You can use unshielded cables on Ethernet ports.

The customer can order a Netra CP2500 RTM-S, build a custom card, or buy from an independent hardware vendor (IHV). A minimal set of I/O must provide for a boot path for the host board, and for a path for console I/O to deliver commands and to read board and system status.

TABLE 1-3 describes the possible Netra CP2500 board boot and I/O configurations. Sun Microsystems provide the Netra CP2500 boards and compatible RTMs. These RTMs provide four Ethernet RJ45 ports from the host to the rear of the system. These ports can optionally be used to accomplish a network boot as a diskless client. The other configurations require IHV hardware.

#### TABLE 1-3 Netra CP2500 Board I/O Configurations

| Hardware Configuration                                 | I/O Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Netra CP2500 board                                     | Serial I/O – Serial port A on the front panel provides the path of the default console I/O.                                                                                                                                                                                                                                                                                                                                                         |

| Netra CP2500 board and<br>RTM-H in a Netra CT server   | Serial I/O – Serial port A can be accessed either from the front of the board or<br>through the RTM-H serial port A, but not both through the front and rear<br>ports at the same time. Serial port B is available through the RTM-H.<br>SCSI – SCSI controller with SCSI I/O routed only to the Netra CT 410 or 810<br>internal drive bays. SCSI PIM I/O is not supported.<br>Ethernet: Four RJ-45 ports on the RTM-H provide Ethernet network I/O |

| Netra CP2500 board and<br>RTM-S in a Netra CT server   | Serial I/O – Serial port A can be accessed either from the front of the board or through the RTM-S serial port A, but not through the front and rear ports at the same time. Serial port B is available through the RTM-S. Ethernet - Four RJ-45 ports on the RTM-S provide Ethernet network I/O.                                                                                                                                                   |

| Netra CP2500 board and RTM-S in a cPSB chassis         | Serial I/O – Serial port A can be accessed either from the front of the board or through the RTM-S serial port A, but not through the front and rear ports at the same time. Serial port B is available through the RTM-S.                                                                                                                                                                                                                          |

|                                                        | <ul> <li>Ethernet – Depends on how you set the mechanical switches on the RTM-S.</li> <li>Switches set to cPSB-mode – Ethernet I/O routed to cPSB network in chassis, and <i>not</i> to the RTM-S RJ-45 ports.</li> <li>Switches set to non-cPSB-mode – Ethernet I/O routed to the four RJ-45 ports on the RTM-S.</li> </ul>                                                                                                                        |

| Optional third-party SCSI or<br>IDE PMC interface card | A third-party PMC interface card can be installed to provide external SCSI, serial, or IDE I/O.                                                                                                                                                                                                                                                                                                                                                     |

# 1.3 Hot-Swap Support

This section briefly discusses the hot-swap support on the Netra CP2500 board.

Refer to the PICMG *CompactPCI Hot-Swap Specification*, for a detailed description of this subject. In general, the hot-swap process includes the orderly connection of the hardware and software.

This process uses hardware connection control to connect the hardware in an orderly sequence. Hot-swapping uses backplane pins of different lengths to perform signal sequencing, which protects the hardware and avoids corrupting the backplane bus.

There are three models of hot-swap described in the PICMG *CompactPCI Hot-Swap Specification* – basic hot-swap, full hot-swap, and high-availability (HA) hot-swap.

TABLE 1-4 lists the hot-swap support details when a Netra CP2500 board is installed in a Netra CT 410 or 810 server, or when the board functions as a cPSB node board in a cPSB enclosure.

| TABLE 1-4 | Netra CP2 | 500 Board | Hot-Swap | Support |

|-----------|-----------|-----------|----------|---------|

|-----------|-----------|-----------|----------|---------|

| Netra CP2500 Role                   | Basic Hot-Swap | Full Hot-Swap | HA Hot-Swap <sup>*</sup> |

|-------------------------------------|----------------|---------------|--------------------------|

| Netra CT 410 or 810 host board      | Yes            | Yes           | Yes <sup>†</sup>         |

| Netra CT 410 or 810 satellite board | Yes            | Yes           | Yes                      |

| cPSB node board                     | Yes            | Yes           | Yes                      |

\* When a board is full hot-swap capable, it implies that the board will also be fully hot-swappable in an HA system.

+ When a board is full hot-swap capable, it implies that the board will also be fully hot-swappable in an HA system.

## 1.4 System Requirements

### 1.4.1 Hardware Requirements

You can order the following items from Sun:

- Netra CP2500 board with 2 Gbytes of memory

- Netra CP2500 CompactPCI satellite/cPSB blade rear transition module (RTM-S)

**Note** – The Netra CP2500 CompactPCI host rear transition module (RTM-H) cannot be ordered separately, but the RTM-H is included the Netra CT 410 and Netra CT 810 Netra CP2500 board upgrade kits.

Rear transition modules are optional and must be ordered separately from the Netra CP2500 board. Refer to the *Netra CP2500 Rear Transition Module Installation and Technical Reference Manual* (819-1753) for complete details about installing and using the Netra CP2500 RTMs.

Acquire the following components if needed:

- Serial terminal or terminal emulation for console output

- Cables for terminal and network connection

Refer to the *Netra CP2500 Rear Transition Module Installation and Technical Reference Manual* (819-1753) for descriptions of the RTM I/O connections.

PMC hardware for additional I/O

TABLE 1-5 lists additional hardware requirements.

| TABLE 1-5 | cPSB System and | Other Minimum | Requirements |

|-----------|-----------------|---------------|--------------|

|-----------|-----------------|---------------|--------------|

| Requirements                                                                                  | Netra CP2500 as Node Board |

|-----------------------------------------------------------------------------------------------|----------------------------|

| cPSB system enclosure for 6U boards (includes chassis, backplane, power supply <sup>*</sup> ) | Yes                        |

| Console output device/serial terminal                                                         | Yes                        |

| Boot device (such as hard drive or network)                                                   | Yes                        |

| Peripheral device for network access                                                          | Yes                        |

| System management controller                                                                  | Yes                        |

\* See Appendix A to ensure that your system enclosure meets the power supply and cooling requirement specifications.

**Caution** – You can damage the Netra CP2500 board components if you install the board in a chassis that does not provide sufficient cooling or has incorrect cPCI I/O voltage (VIO).

**Note** – If you will be updating the host or satellite CompactPCI boards in a Netra CT 410 or 810 server, refer to the *Netra CT Server Upgrade Guide* (819-2745) for the hardware requirements.

## 1.4.2 Software Requirements

Refer to the *Netra CP2500 Board Release Notes* (819-1748) for Solaris OS information, including a list of the required software patches and where to find installation instructions. You can view and download the latest version of this document at the following web site:

http://www.sun.com/documentation/

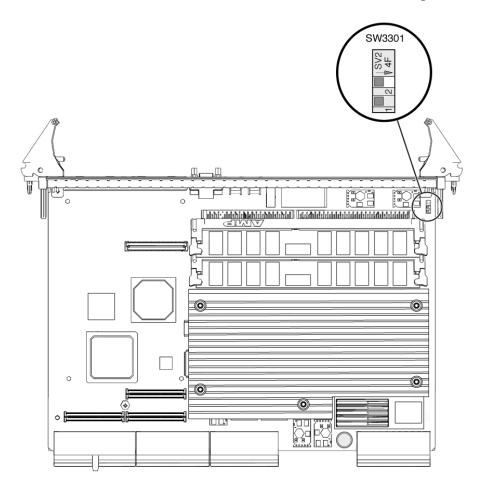

# 1.5 Physical Description

The Netra CP2500 board is a 6U circuit board with CompactPCI connectors J1 and J2 for PCI, and J3 and J5 for I/O. The CompactPCI J4 connector is not fitted to the board. See FIGURE 1-8 and FIGURE 1-9 for top and solder-side views of the board.

**Note** – The heat sink is not shown in this diagram to illustrate the components on the board that lie beneath the heat sink.

FIGURE 1-8 Netra CP2500 Board Layout

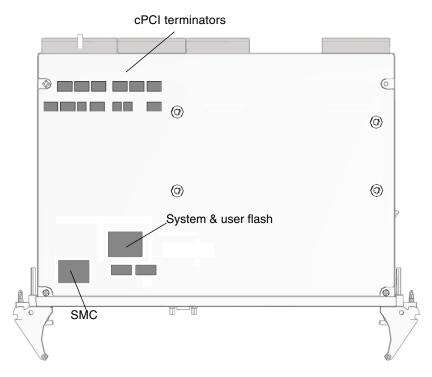

FIGURE 1-9 Typical Netra CP2500 Board – Solder Side

## 1.5.1 Front Panel Components

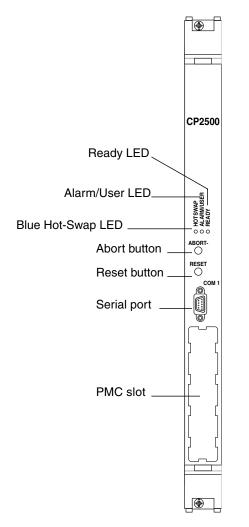

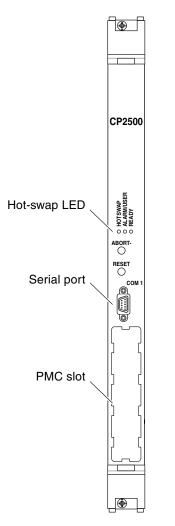

FIGURE 1-10 displays the locations of the Netra CP2500 board front panel LEDs, buttons, serial port, and PMC slot. TABLE 1-6 describes these front panel components.

FIGURE 1-10 Netra CP2500 Board Front Panel

### TABLE 1-6Front Panel I/O

| Front panel component | Description                                                                                                                                                                                                                                                                                        |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ready green LED       | A green LED showing that the board is receiving power, which<br>is sourced from the power module and controlled by the system<br>management controller (SMC).                                                                                                                                      |  |

| Alarm/User yellow LED | You can define the operation of this yellow LED. The default function of this LED shows that the board is at an OK status. The colors are CPU controlled by way of the SMC. Refer to the <i>Netra CP2500 Board Programming Guide</i> (819-1749) for information on programming the alarm/user LED. |  |

| Hot-swap blue LED     | A blue LED that shows the hot-swap status of the board. See<br>Section 3.1, "Hot-Swap Information" on page 3-2 for more<br>information about hot-swap operations.<br><b>Note</b> - The hot-swap LED is in a noncompliant location of the<br>front panel.                                           |  |

| Abort button          | An abort button, which passes an externally initiated reset (XIR) signal to the SMC when pressed.                                                                                                                                                                                                  |  |

| Reset button          | A reset button, which passes an power-on-reset (POR) signal to the SMC when pressed.                                                                                                                                                                                                               |  |

| Serial port (COM1)    | One micro DB9 connector is available for serial port (TTYA) I/O. This port can only be used if rear serial port COM A is not being used.                                                                                                                                                           |  |

| PMC slot              | One peripheral mezzanine card (PMC) slot is available for additional I/O.                                                                                                                                                                                                                          |  |

### 1.5.2 Functional Block Diagram

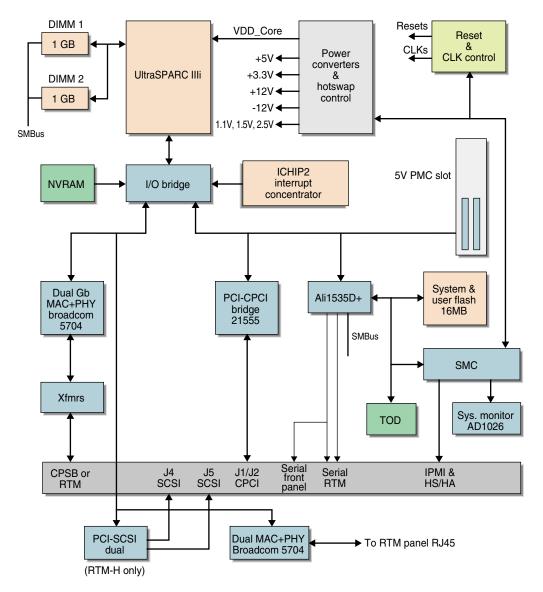

FIGURE 1-11 displays a simplified schematic diagram of the Netra CP2500 board.

FIGURE 1-11 Netra CP2500 Board Functional Block Diagram

# 1.6 Contacting Technical Support

Should you have any technical questions or support issues that are not addressed in the Netra CP2500 documentation set or on the web site, contact your local Sun Services representative. Find the World Wide Solution Center nearest you by visiting our web site:

http://www.sun.com/service/contacting/solution.html

When you call Sun Services, be sure to indicate if the Netra CP2500 board was purchased separately and is not associated with a system. Please have your Sun support contract number and the board identification information ready when you call. For proper identification of the board be prepared to give the representative the board part number, serial number, and board revision level (see FIGURE 1-12).

### 1.6.1 Board Identification

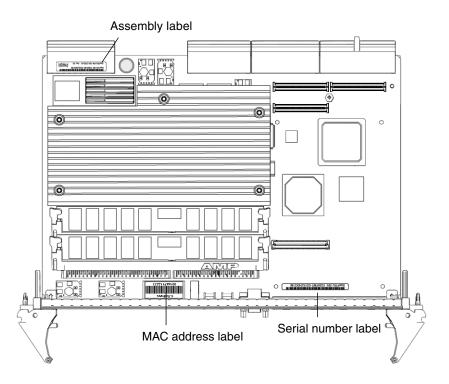

The Netra CP2500 board can be identified by the barcode labels placed on the board (see FIGURE 1-12). You will need to locate the following labels to identify the board properly:

- Serial number barcode label provides the board's serial number (for example, 1005LCB-0532JM000V).

- Assembly label contains the board's part number, the revision number (for example, Rev. 04), and the country where the board was assembled.

- MAC address label displays the MAC address for the board in printed and barcode form. See Section 2.5.3, "Replacing the SEEPROM" on page 2-13 for information on replacing the SEEPROM.

FIGURE 1-12 Typical Netra CP2500 Board Barcode Labeling

**Note** – You might find the labels shown in FIGURE 1-12 on other locations on your board. Also, your board configuration might appear different than shown in the preceding illustration.

# Installing the Netra CP2500 Board in a cPSB Chassis

This chapter describes how to install a Netra CP2500 board hardware in a cPSB chassis.

**Note** – This chapter does *not* describe how to install the board in a Netra CT 410 or 810 server, or how to replace a Netra CP2300 cPSB board installed in a cPSB chassis. See Section 2.1, "Installation Options" on page 2-2 for more information.

This chapter contains the following sections:

- Section 2.1, "Installation Options" on page 2-2

- Section 2.2, "Equipment and Operator Safety" on page 2-3

- Section 2.3, "Materials and Tools Required" on page 2-4

- Section 2.4, "Preparing for the Installation" on page 2-4

- Section 2.5, "Configuring the Board Hardware" on page 2-7

- Section 2.6, "Installing Boards Into a cPSB Chassis" on page 2-19

- Section 2.7, "Setting Up an Assembled Netra CP2500 Board" on page 2-22

- Section 2.8, "Initial Power On and Firmware Upgrade" on page 2-23

## 2.1 Installation Options

This chapter describes how to install the Netra CP2500 board in a cPSB chassis. TABLE 2-1 lists other installation options and where you can find the installation procedures.

| TABLE 2-1 Hardware | Installation | Options |

|--------------------|--------------|---------|

|--------------------|--------------|---------|

| Installation Option                                                   | Installation Procedure Location                                                                                           |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Upgrading the host or satellite board in a Netra CT 410 or 810 server | Refer to the <i>Netra CT Server Upgrade Guide</i> (819-2745) for the upgrade procedures.                                  |  |

| Installing a new satellite board in a Netra CT 410 or 810 server      | Refer to the <i>Netra CT Server Installation Guide</i> (819-2740) for these procedures.                                   |  |

| Replacing a defective board in a Netra CT 410 or 810 server           | Refer to the <i>Netra CT Server System Administration Guide</i> (819-2741) for these removal and installation procedures. |  |

| Installing the board in the Netra CT 820 cPSB server                  | The Netra CP2500 board is not supported in the Netra CT 820 server.                                                       |  |

| Installing the board in a third-party cPSB chassis                    | This chapter describes how to install the board in a third-party cPSB chassis.                                            |  |

You can download PDF and HTML versions of Sun documentation at the following web site:

http://www.sun.com/documentation/

**Note** – While the Netra CP2500 board can operate as a CompactPCI host or satellite CPU board in the Netra CT 410 and 810 servers, the board is *not* supported in third-party CompactPCI systems or chassis.

## 2.2 Equipment and Operator Safety

Refer to the *Important Safety Information for Sun Hardware Systems* (816-7190) for general safety information.

Read these safety statements specific to the Netra CP2500 board carefully before you install or remove any part of the system.

**Caution** – Depending on the particular chassis design, operations with open equipment enclosures can expose the installer to hazardous voltages with a consequent danger of electric shock. Ensure that line power to the equipment is disconnected during operations that make high voltage conductors accessible.

The installer must be familiar with commonly-accepted procedures for integrating electronic systems and with the general practice of Sun systems integration and administration. Although parts of these systems are designed for hot-swap operation, other components must not be subjected to such stresses. Work with power connected to a chassis only when necessary and follow these installation procedures to avoid equipment damage.

This equipment is sensitive to damage from electrostatic discharge (ESD) from clothing and other materials. Use the following antistatic measures during an installation:

- If possible, disconnect line power from the equipment chassis when servicing a system or installing a hardware upgrade. If the chassis cannot be placed upon a grounded antistatic mat, connect a grounding strap between the facility electrical input ground (usually connected to the equipment chassis) and facility electrical service ground.

- Use an antistatic wrist strap when:

- Removing a board from its antistatic bag

- Connecting or disconnecting boards or peripherals

Connect the other end of the strap lead to one of the following:

- A ground mat

- Grounded chassis metalwork

- A facility electrical service ground

- Keep boards in the antistatic bags until they are needed.

- Place circuit boards that are out of their antistatic bags on an antistatic mat if one is available. The mat must be grounded to a facility electrical service ground. Do not place boards on top of an antistatic bag unless the outside of the bag also has antistatic protective properties.

- Remove a board from its antistatic bag only when wearing a properly connected ground strap.

## 2.3 Materials and Tools Required

This section provides information on the materials and tools required to perform installation. The minimum tools required to perform installation are:

- Straight blade screwdriver, 1/4 inch

- Phillips screwdrivers, No. 1, No. 2

- Antistatic wrist strap

- Needle nose pliers

- Needle, metal pick, scribe tool, or small screwdriver to set the DIP switches

- Terminal

Refer to Section 1.4.1, "Hardware Requirements" on page 1-13 for information on hardware requirements.

## 2.4 Preparing for the Installation

Read the following subsections before starting to install these boards. In addition, do the following:

- 1. Become familiar with the contents of the referenced documentation.

- 2. Verify that all listed hardware and software is available (see Section 1.4, "System Requirements" on page 1-13).

- 3. Check power, thermal, environmental, and space requirements (see Section 2.4.1, "Checking Power, Thermal, Environmental, and Space Requirements" on page 2-5).

- 4. Verify that local area networking (LAN) preparations are completed (see Section 2.4.2, "Determining Local Network IP Addresses and Hostnames" on page 2-5).

- 5. Ensure that the host names and their network IP addresses are allocated and registered at the site.

## 2.4.1 Checking Power, Thermal, Environmental, and Space Requirements

Ensure that:

- Your enclosure specifications support the sum of the specified maximum board power loads. See Section A.4, "Power Requirements" on page A-3 for board power specifications.

- Facility power loading specifications can support the rack or enclosure requirements.

- Your enclosure specifications support the cooling airflow requirements. See Section A.6, "Environmental Specifications" on page A-6.

- The Netra CP2500 board fits a standard CompactPCI packet switched backplane (cPSB) chassis. If your installation requirements are different, contact your field application engineer.

## 2.4.2 Determining Local Network IP Addresses and Hostnames

Collect the following information to connect hosts to the local area network (LAN). Ask your network administrator for help, if necessary. This information is not needed for a standalone installation. You can use TABLE 2-2 to record this information.

| Information Needed                                                                                                   | Your Information |

|----------------------------------------------------------------------------------------------------------------------|------------------|

| IP addresses <sup>*</sup> and hostname for each Netra<br>CP2500 client                                               |                  |

| Domain name                                                                                                          |                  |

| Type of name service and corresponding<br>name server names and IP addresses – for<br>example, DNS and NIS (or NIS+) |                  |

| Subnet mask                                                                                                          |                  |

| Gateway router IP address                                                                                            |                  |

| NFS server names and IP addresses                                                                                    |                  |

| Web server URL                                                                                                       |                  |

TABLE 2-2

Your Local Network Information

You might need the MAC addresses of the local hosts to make nameserver database entries. The MAC address can be seen in the console output while booting to the ok prompt. It can also be derived from the host ID seen on the barcode label of the SEEPROM (see Section 1.6.1, "Board Identification" on page 1-20).

#### 2.4.3 Installation Procedure Summary

**Note** – This chapter does *not* describe how to install the board in a Netra CT 410 or 810 server, or how to replace a Netra CP2500 cPSB board installed in a cPSB chassis. See Section 2.1, "Installation Options" on page 2-2 for more information.

This section summarizes the Netra CP2500 board installation at a high level. Ensure that you read the details in Section 2.5, "Configuring the Board Hardware" on page 2-7 through Chapter 3 before installing the board.

The process to set up and configure a Netra CP2500 board in a cPSB chassis includes the following steps:

1. Configure the board's physical hardware.

For example, install the PMC card, replace the SEEPROM (if required), and set DIP switches if necessary.

- 2. If your environment requires rear access to connect cables, configure and install the RTM-S module.

- a. Configure the RTM-S module.

For example, set DIP switch settings or prepare connector attachments, as necessary.

- b. Physically install the RTM-S.

- 3. Physically install the Netra CP2500 board, and any peripheral boards, into the chassis.

- 4. Connect the node(s) to a local network. Alternatively, the board can be run as a standalone system without a network connection.

- 5. Install the Solaris Operating System.

## 2.5 Configuring the Board Hardware

This section lists hardware installation and settings that might apply for your board configuration. Read and perform the procedures, as necessary, before installing the Netra CP2500 board into a cPSB chassis.

#### 2.5.1 Installing an Optional PMC Device

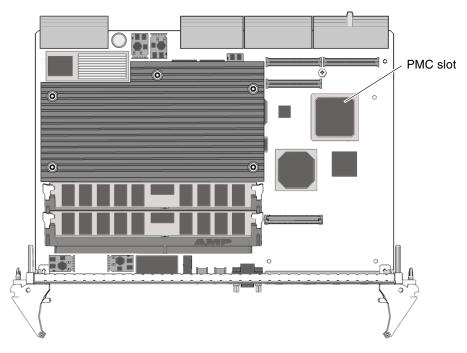

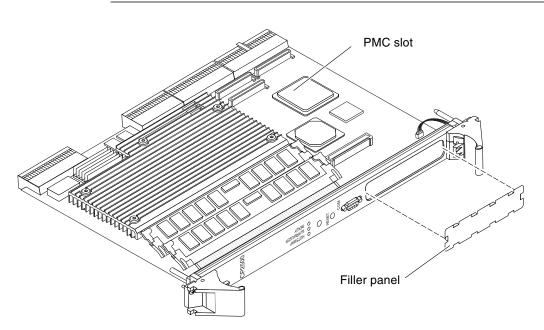

A PCI mezzanine card (PMC) is a slim, modular mezzanine card that provides additional functionality to the Netra CP2500 board. The board contains one PMC slot in which you can install an optional PMC device (see FIGURE 2-1 for the location of the slot). You must install PMC devices on the Netra CP2500 board before you install the board into the chassis.

FIGURE 2-1 PMC Slot Location

**Note** – Before installing the PMC device, ensure that the device is keyed to 5V, or is set to universal voltage.

**Note** – The following procedure provides a generic set of instructions for installing PMC devices on the Netra CP2500 board. Refer to the PMC card manufacturer's documentation for specific instructions on installing these devices.

- 1. Retrieve the wrist strap from the adapter's shipping kit.

- 2. Attach the antistatic wrist strap:

- a. Attach the adhesive copper strip of the wrist strap to the metal chassis.

- b. Wrap the other end twice around your wrist, with the adhesive side against your skin.

- 3. Remove the Netra CP2500 board from its antistatic envelope and place it on an ESD mat (if one is available) near the chassis.

If an ESD mat is not available, you can place the card on the antistatic envelope it was packaged in.

**Note** – If EMI compliance is required, do not remove the PMC filler panel unless you are going to install a PMC on the board.

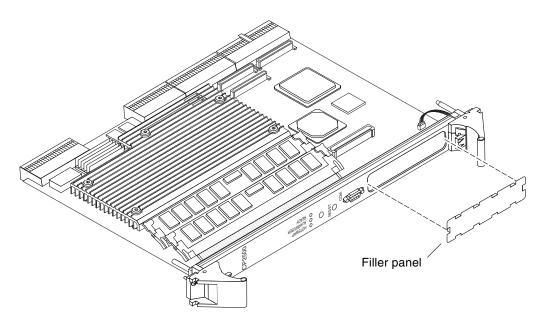

## 4. If the PMC has a connector for cabling, or if the PMC has a faceplate that fits in the Netra CP2500 board's faceplate, remove the board's filler panel (FIGURE 2-2).

Depending on its application, a PMC might contain a connector where you need to attach a PMC-specific cable, or it might have LEDs that must be viewed while the operating. If the PMC has a connector, LEDs, or a protruding faceplate, remove the board's filler panel.

FIGURE 2-2 Removing the PMC Filler Panel

- 5. Retrieve the PMC from its shipping kit and place it on an antistatic surface.

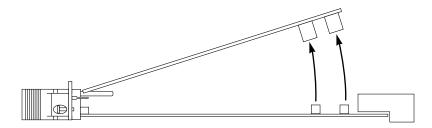

- **6. Insert the PMC at an angle into the appropriate PMC slot (**FIGURE 2-3)**.** Ensure that the PMC's connector goes through the board's PMC slot.

FIGURE 2-3 Inserting the PMC Into the PMC Slot

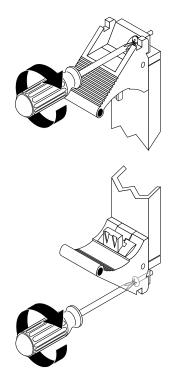

- 7. Align the PMC over the PMC connectors.

- 8. Carefully press the PMC into the board's PMC connectors (FIGURE 2-4).

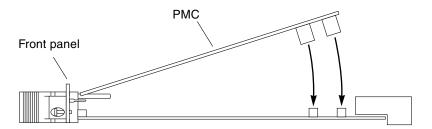

FIGURE 2-4 Pressing the PMC Into the PMC Connectors – Side View

**Caution** – Do not use excessive force when installing the PMC into the slot. You might damage the PMC's connectors or the connectors on the Netra CP2500 board, causing permanent damage to the PMC or the board. If the PMC does not seat properly when you apply even pressure, remove the PMC and carefully reinstall it.

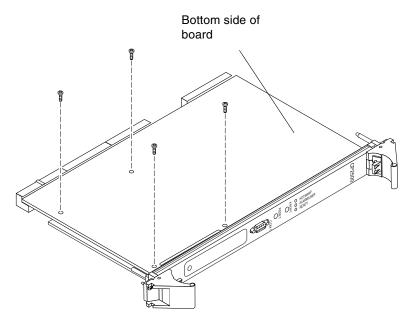

9. Turn the Netra CP2500 board over and use a No. 1 screwdriver to secure the four screws that attach the PMC to the Netra CP2500 board (FIGURE 2-5).

FIGURE 2-5 Securing the PMC Screws

Refer to the PMC device's documentation for PMC software and cabling installation instructions.

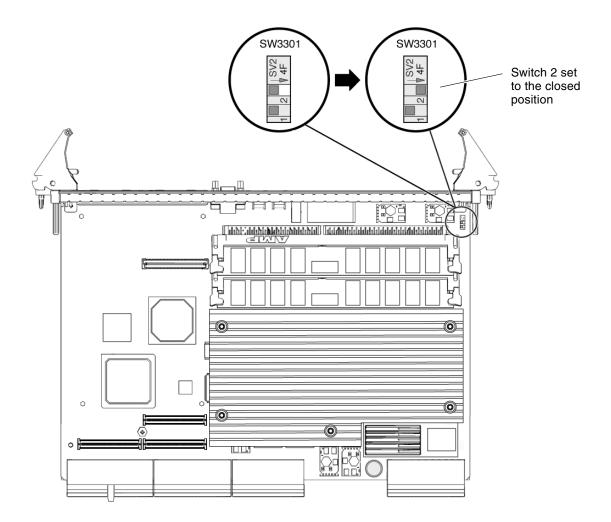

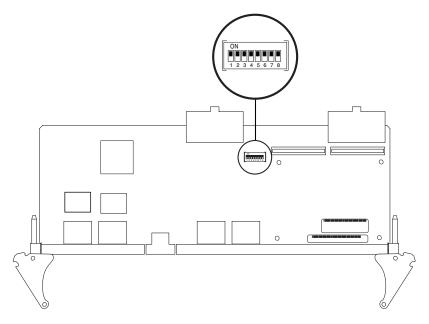

#### 2.5.2 Setting the SW3301 DIP Switch

Switch 2 of the SW3301 DIP switch bank selects whether the board will operate in a Netra CT 410 or 810 CompactPCI server or in a cPSB chassis. By default, this switch is set so that the board will operate in a Netra CT 410 or 810 server. Prior to installing the Netra CP2500 board into a cPSB chassis, you must change the setting of this switch so that the board will operate in a cPSB chassis.

**Note** – See Section B.4, "DIP Switch Settings" on page B-18, for further details about the Netra CP2500 board switch settings.

To Set SW3301 Switch 2 to cPSB operation:

- 1. Retrieve the wrist strap from the adapter's shipping kit.

- 2. Attach the antistatic wrist strap:

- a. Attach the adhesive copper strip of the wrist strap to the metal chassis.

- b. Wrap the other end twice around your wrist, with the adhesive side against your skin.

- 3. Remove the Netra CP2500 board from its antistatic envelope and place it on an ESD mat (if one is available) near the chassis.

If an ESD mat is not available, you can place the card on the antistatic envelope it was packaged in.

4. Using a needle, metal pick, scribe tool, or a small screwdriver, set switch 2 from the open position (in the direction opposite of the arrow on the switch) to closed (in the direction of the arrow).

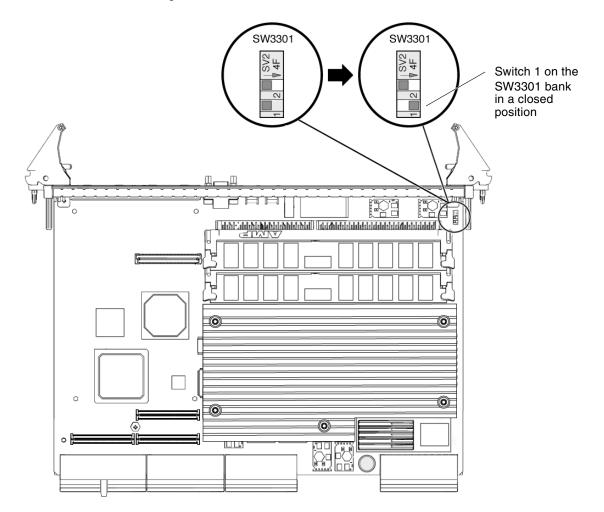

The SW3301 DIP switch bank is located on the component side of the board between the front panel and heat sink (see FIGURE 2-6). FIGURE 2-6 displays how to set switch 2 from the open to closed position.

FIGURE 2-6 Setting the SW3301 Switch 2 to cPSB Chassis Operation

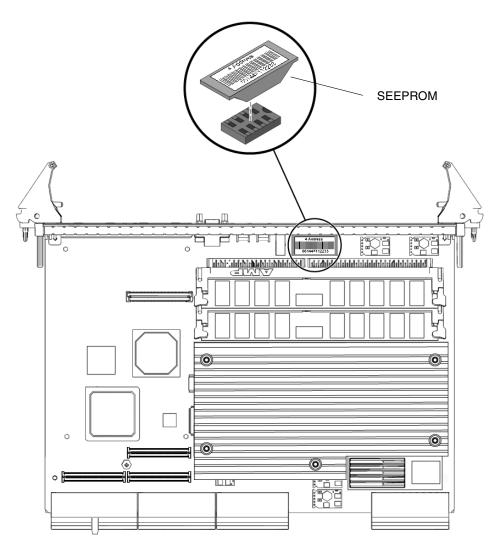

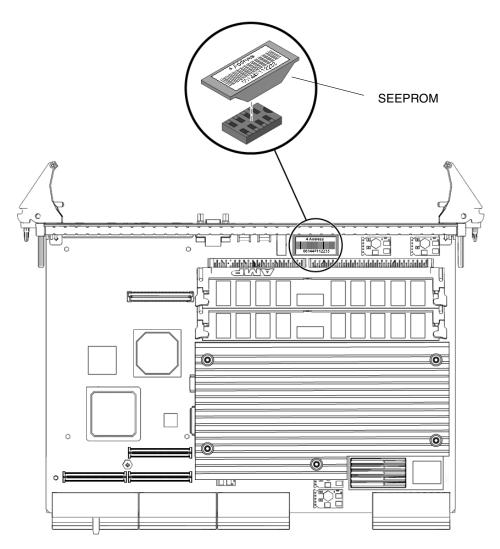

#### 2.5.3 Replacing the SEEPROM

The SEEPROM stores the board MAC address and host ID information. You do not need to replace the SEEPROM unless you are installing a replacement board that does not have the correct host ID information.

If you need to replace the Netra CP2500 board, remove the SEEPROM from the original board and install it on the replacement Netra CP2500 board.

To Replace the SEEPROM:

- 1. Retrieve the wrist strap from the adapter's shipping kit.

- 2. Attach the antistatic wrist strap:

- a. Attach the adhesive copper strip of the wrist strap to the metal chassis.

- b. Wrap the other end twice around your wrist, with the adhesive side against your skin.

- 3. Remove the Netra CP2500 board from its antistatic envelope and place it on an ESD mat (if one is available) near the chassis.

If an ESD mat is not available, you can place the card on the antistatic envelope it was packaged in.

4. Locate the MAC address label on the board.

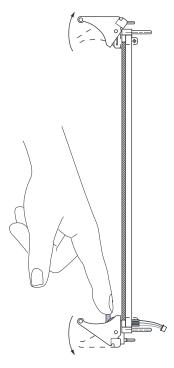

The MAC address label is located between the board's faceplate and the memory connectors (see FIGURE 2-7). The MAC address label is fastened on a plastic carrier that protects the SEEPROM.

5. Carefully lift the plastic SEEPROM carrier off of the board (see FIGURE 2-7).

Removing the plastic contain will also remove the board's SEEPROM.

FIGURE 2-7 Replacing the SEEPROM

6. Locate the SEEPROM that you removed from the original, defective board you returned to Sun Services.

The SEEPROM should still be encased in its protective plastic carrier with its MAC address label attached.

7. Carefully press the SEEPROM carrier on the board.

#### 2.5.4 Preparing the RTM-S for Installation

If you are using the Netra CP2500 RTM-S, refer to the *Netra CP2500 Rear Transition Module Installation and Technical Reference Manual* (819-1753). You might also want to refer to this RTM manual for detailed connector pin assignments.

**Note** – An RTM is not required to operate Netra CP2500 board. However, an RTM is needed if you will be connecting cables to the rear of the system or chassis.

#### 2.5.4.1 Differences Between Available Netra CP2500 Rear Transition Modules

Two rear transition modules are available from Sun for the Netra CP2500 board – the RTM-H and the RTM-S. The RTM-H is designed to be operated solely in the host CompactPCI slot of the Netra CT 410 and 810 servers. The RTM-H will not operate in a cPSB chassis, and it is not supported in any other CompactPCI server.

The RTM-S card can operate in either a Netra CT 410 or 810 server satellite slot or in a node slot of cPSB chassis. When installing a Netra CP2500 board into a cPSB chassis, you must use either this RTM-S or a custom-designed RTM.

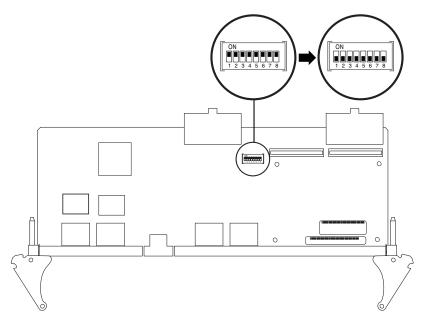

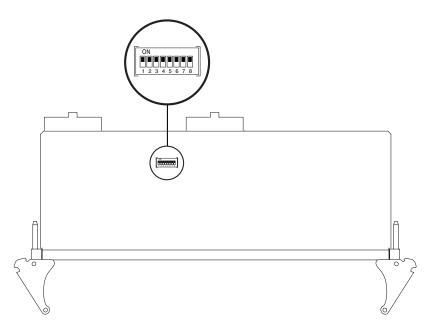

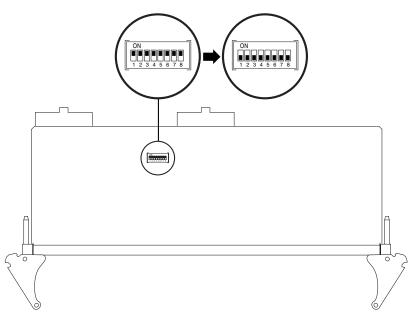

#### 2.5.4.2 Setting RTM-S DIP Switches

The Netra CP2500 RTM-S contains two DIP switch banks that must be set prior to installing the card into the cPSB chassis. These switch banks control whether the Ethernet network traffic of the board is routed to the RJ45 connectors on the RTM-S or whether the RTM-S runs in cPSB mode and the Ethernet network traffic is routed to the cPSB backplane. By default, these switch banks are set to route the traffic to the RJ45 connectors. Therefore, before installing the RTM-S into a cPSB chassis, set these switches to cPSB network operation.

**Note** – For additional information about these DIP switch settings, refer to the *Netra CP2500 Rear Transition Module Installation And technical Reference Manual* (819-1753).

To set the RTM-S DIP switches to cPSB network operation:

#### 1. Retrieve the wrist strap from the adapter's shipping kit.

- 2. Attach the antistatic wrist strap: