SPARC: Relocation Entries

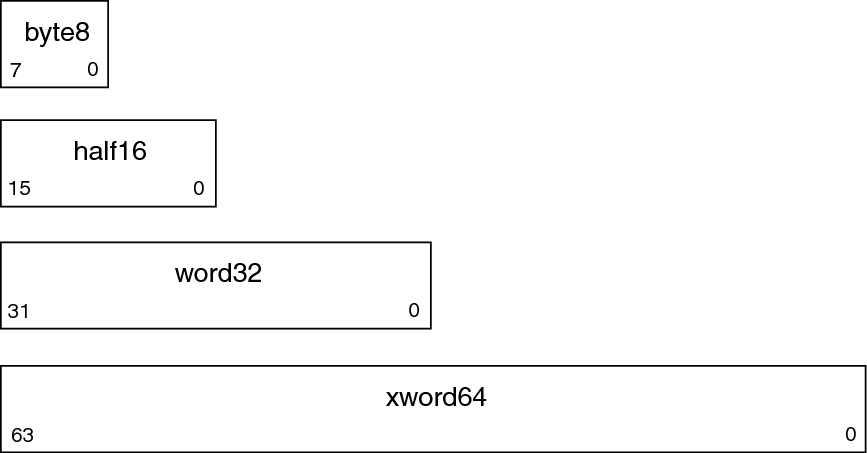

On the SPARC platform, relocation entries apply to bytes (byte8),

half-words (half16), words (word32), and

extended-words (xword64).

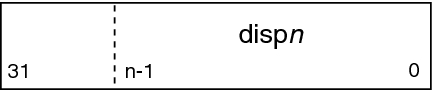

The dispn

family of relocation fields

(disp19, disp22, disp30) are

word-aligned, sign-extended, PC-relative displacements. All encode a value with its least

significant bit in position 0 of the word, and differ only in the number of bits allocated

to the value.

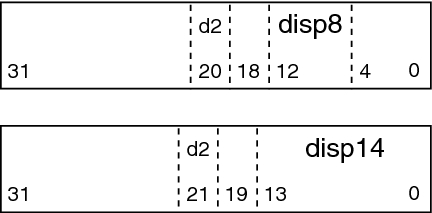

The d2/disp8 and d2/disp14 variants encode 16 and

10-bit displacement values using two non-contiguous bit fields, d2, and

dispn

.

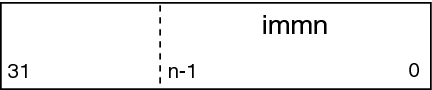

The immn family of relocation fields

(imm5, imm6, imm7,

imm10, imm13, imm22) represent

unsigned integer constants. All encode a value with its least significant bit in position 0

of the word, and differ only in the number of bits allocated to the value.

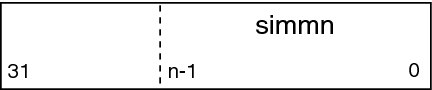

The simmn

family of relocation fields

(simm10, simm11, simm13,

simm22) represent signed integer constants. All encode a value with its

least significant bit in position 0 of the word, and differ only in the number of bits

allocated to the value.