| A P P E N D I X D |

Memory Module (DIMM) Reference

Memory Module (DIMM) Reference |

When replacing or upgrading a DIMM on the Sun Blade X6270 M2 Server Module, see the following sections:

The Sun Blade X6270 M2 Server Module supports a variety of DIMM configurations that can include single-rank (SR) DIMMs, dual-rank (DR) DIMMs, or quad-rank (QR) DIMMs. When replacing or adding memory modules to the Sun Blade X6270 M2 Server Module, you should consider the following:

For details, see DIMM and CPU Physical Layout.

For details, see DIMM Population Rules.

For details, see DIMM Rank Classification Labels.

For details, see Error Correction and Parity

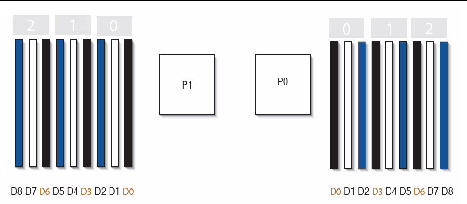

The physical layout of the DIMMs and CPUs on a Sun Blade X6270 M2 Server Module is shown in FIGURE D-1.

FIGURE D-1 CPU and DIMM Physical Layout

The DIMM population rules for the Sun Blade X6270 M2 Server Module are as follows:

1. Do not populate any DIMM socket next to an empty CPU socket. Each processor contains a separate memory controller.

2. Each CPU can support a maximum of:

3. Each CPU can support single DIMMs or two DIMMs per channel.

4. Each CPU can support a single DIMM in channel 0, or one DIMM each in channels 0 and 1.

5. A server CPU will support both 1.35v and 1.5v DIMMs, but will default to the higher voltage.

6. Populate DIMMs by location according to the following rules:

For example, populate D8/D5/D2 first; then D7/D4/D1 second; and finally, D6/D3/D0. See FIGURE D-1.

Note that QR DIMMs are supported only in white sockets if adjacent blue socket contains a QR DIMM.

7. For maximum performance, apply the following rules:

DIMMs come in a variety of ranks: single, dual, or quad. Each DIMM is shipped with a label identifying its rank classification. TABLE D-2 identifies the corresponding rank classification label shipped with each DIMM.

The server’s processor provides parity protection on its internal cache memories and error-correcting code (ECC) protection of the data. The system can detect and log the following types of errors:

Advanced ECC corrects up to 4 bits in error on nibble boundaries, as long as they are all in the same DRAM. If a DRAM fails, the DIMM continues to function.

Refer to the Oracle Integrated Lights Out Manager (ILOM) 3.0 Documentation Collection for information on how to access the error log.

When a single DIMM is marked as faulty by ILOM (for example, fault.memory.intel.dimm.training-failed is listed in the SP Event Log), BIOS might map out the entire memory channel that contains the faulty DIMM as failing, that is, up to three DIMMs. As a result, the memory available to the operating system is reduced.

However, when the Fault Remind button is pressed, only the fault LED associated with the faulty DIMM lights. The fault LEDs for the other two DIMMs in the memory channel remain off. Therefore, you can correctly identify the faulty DIMM. When the faulty DIMM is replaced and the DIMM fault is cleared using ILOM, the memory available to the operating system returns to normal. For instructions for clearing DIMM faults, see the Oracle Integrated Lights Out Manager (ILOM) 3.0 Supplement for the Sun Blade X6270 M2 Server Module (821-0501).

ILOM and BIOS use different formats to identify the location of a faulty DIMM.

TABLE D-3 shows the mapping of faulty DIMM locations as reported by ILOM and BIOS.

Copyright © 2012, Oracle and/or its affiliates. All rights reserved.