| Skip Navigation Links | |

| Exit Print View | |

|

Writing Device Drivers Oracle Solaris 11 Express 11/10 |

| Skip Navigation Links | |

| Exit Print View | |

|

Writing Device Drivers Oracle Solaris 11 Express 11/10 |

Part I Designing Device Drivers for the Oracle Solaris Platform

1. Overview of Oracle Solaris Device Drivers

2. Oracle Solaris Kernel and Device Tree

5. Managing Events and Queueing Tasks

7. Device Access: Programmed I/O

10. Mapping Device and Kernel Memory

13. Hardening Oracle Solaris Drivers

14. Layered Driver Interface (LDI)

Part II Designing Specific Kinds of Device Drivers

15. Drivers for Character Devices

18. SCSI Host Bus Adapter Drivers

19. Drivers for Network Devices

Part III Building a Device Driver

21. Compiling, Loading, Packaging, and Testing Drivers

22. Debugging, Testing, and Tuning Device Drivers

23. Recommended Coding Practices

PCI Configuration Address Space

PCI Configuration Base Address Registers

PCI Hardware Configuration Files

SBus Hardware Configuration Files

B. Summary of Oracle Solaris DDI/DKI Services

C. Making a Device Driver 64-Bit Ready

This section describes a number of SPARC processor-specific topics such as data alignment, byte ordering, register windows, and availability of floating-point instructions. For information on x86 processor-specific topics, see x86 Processor Issues.

Note - Drivers should never perform floating-point operations, because these operations are not supported in the kernel.

All quantities must be aligned on their natural boundaries, using standard C data types:

short integers are aligned on 16-bit boundaries.

int integers are aligned on 32-bit boundaries.

long integers are aligned on 64-bit boundaries for SPARC systems. For information on data models, see Appendix C, Making a Device Driver 64-Bit Ready.

long long integers are aligned on 64-bit boundaries.

Usually, the compiler handles any alignment issues. However, driver writers are more likely to be concerned about alignment because the proper data types must be used to access the devices. Because device registers are commonly accessed through a pointer reference, drivers must ensure that pointers are properly aligned when accessing the device.

Because of the data alignment restrictions imposed by the SPARC processor, C structures also have alignment requirements. Structure alignment requirements are imposed by the most strictly aligned structure component. For example, a structure containing only characters has no alignment restrictions, while a structure containing a long long member must be constructed to guarantee that this member falls on a 64-bit boundary.

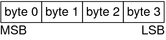

The SPARC processor uses big-endian byte ordering. The most significant byte (MSB) of an integer is stored at the lowest address of the integer. The least significant byte is stored at the highest address for words in this processor. For example, byte 63 is the least significant byte for 64-bit processors.

SPARC processors use register windows. Each register window consists of eight in registers, eight local registers, eight out registers, and eight global registers. Out registers are the in registers for the next window. The number of register windows ranges from 2 to 32, depending on the processor implementation.

Because drivers are normally written in C, the compiler usually hides the fact that register windows are used. However, you might have to use register windows when debugging the driver.

The Version 7 SPARC processors do not have multiply or divide instructions. The multiply and divide instructions are emulated in software. Because a driver might run on a Version 7, Version 8, or Version 9 processor, avoid intensive integer multiplication and division. Instead, use bitwise left and right shifts to multiply and divide by powers of two.

The SPARC Architecture Manual, Version 9, contains more specific information on the SPARC CPU. The SPARC Compliance Definition, Version 2.4, contains details of the application binary interface (ABI) for SPARC V9. The manual describes the 32-bit SPARC V8 ABI and the 64-bit SPARC V9 ABI. You can obtain this document from SPARC International at http://www.sparc.com.