Hardware Overview

This appendix discusses general issues about hardware that is capable of supporting the Oracle Solaris OS. The discussion includes the processor, bus architectures, and memory models that are supported by the operating system. Various device issues and the PROM used in Oracle platforms are also covered.

Note - The material in this appendix is for informational purposes only. This information might be of use during driver debugging. However, many of these implementation details are hidden from device drivers by the Oracle Solaris DDI/DKI interfaces.

This appendix provides information about the following subjects:

SPARC Processor Issues

This section describes a number of SPARC processor-specific topics such as data alignment, byte ordering, register windows, and availability of floating-point instructions. For information about x86 processor-specific topics, see x86 Processor Issues.

Note - Drivers should never perform floating-point operations, because these operations are not supported in the kernel.

SPARC Data Alignment

short integers are aligned on 16-bit boundaries.

int integers are aligned on 32-bit boundaries.

long integers are aligned on 64-bit boundaries for SPARC systems. For information about data models, see Making a Device Driver 64-Bit Ready.

long long integers are aligned on 64-bit boundaries.

All quantities must be aligned on their natural boundaries, using standard C data types:

Usually, the compiler handles any alignment issues. However, driver writers are more likely to be concerned about alignment because the proper data types must be used to access the devices. Because device registers are commonly accessed through a pointer reference, drivers must ensure that pointers are properly aligned when accessing the device.

Member Alignment in SPARC Structures

Because of the data alignment restrictions imposed by the SPARC processor, C structures also have alignment requirements. Structure alignment requirements are imposed by the most strictly aligned structure component. For example, a structure containing only characters has no alignment restrictions, while a structure containing a long long member must be constructed to guarantee that this member falls on a 64-bit boundary.

SPARC Byte Ordering

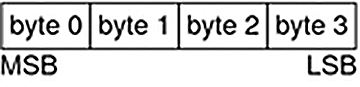

The SPARC processor uses big-endian byte ordering. The most significant byte (MSB) of an integer is stored at the lowest address of the integer. The least significant byte is stored at the highest address for words in this processor. For example, byte 63 is the least significant byte for 64-bit processors.

SPARC Register Windows

SPARC processors use register windows. Each register window consists of eight in registers, eight local registers, eight out registers, and eight global registers. Out registers are the in registers for the next window. The number of register windows ranges from 2 to 32, depending on the processor implementation.

Because drivers are normally written in C, the compiler usually hides the fact that register windows are used. However, you might have to use register windows when debugging the driver.

SPARC Multiply and Divide Instructions

The SPARC Architecture Manual, Version 9, contains more specific information about the SPARC CPU. SPARC Compliance Definition, Version 2.4, contains details of the application binary interface (ABI) for SPARC V9. The manual describes the 32-bit SPARC V8 ABI and the 64-bit SPARC V9 ABI. For information about Oracle SPARC processor, see SPARC Servers Documentation. You can obtain this document from SPARC International at http://sparc.org/technical-documents/.