| ナビゲーションリンクをスキップ | |

| 印刷ビューの終了 | |

|

デバイスドライバの記述 Oracle Solaris 11.1 Information Library (日本語) |

| ナビゲーションリンクをスキップ | |

| 印刷ビューの終了 | |

|

デバイスドライバの記述 Oracle Solaris 11.1 Information Library (日本語) |

パート I Oracle Solaris プラットフォーム用デバイスドライバの設計

2. Oracle Solaris カーネルとデバイスツリー

22. ドライバのコンパイル、ロード、パッケージ化、およびテスト

23. デバイスドライバのデバッグ、テスト、およびチューニング

このセクションでは、Oracle Solaris プラットフォームがサポートしているバスに固有の、アドレス指定とデバイス構成の問題について説明します。

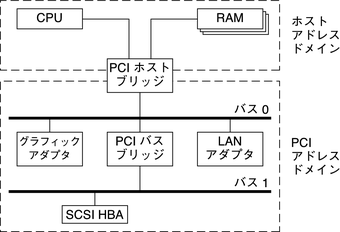

PCI ローカルバスは、高速なデータ転送のために設計された高性能なバスです。PCI バスは、システムボード上にあります。このバスは通常、高度に統合された周辺コンポーネント、周辺アドオンボード、およびホストプロセッサまたはメモリーシステムの間の相互接続機構として使用されます。ホストプロセッサ、メインメモリー、および PCI バス自体は、図 A-3 に示すように、PCI ホストブリッジを介して接続されます。

相互に接続された I/O バスのツリー構造は、一連の PCI バスブリッジを介してサポートされます。下位の PCI バスブリッジを PCI ホストブリッジの下で拡張し、単一のバスシステムを拡張して、複数のセカンダリバスを持つ複雑なシステムにできます。PCI デバイスは、これらの 1 つ以上のセカンダリバスに接続できます。また、SCSI や USB などのほかのバスブリッジも接続できます。

すべての PCI デバイスには、一意なベンダー ID とデバイス ID があります。同じ種類の複数のデバイスは、デバイスが存在するバスの一意のデバイス番号によってさらに識別されます。

PCI ホストブリッジによって、プロセッサと周辺コンポーネントが相互に接続されます。プロセッサは、PCI ホストブリッジを介して、ほかの PCI バスマスターから独立して直接メインメモリーにアクセスできます。たとえば、CPU がホストブリッジのキャッシュコントローラからデータを取得している間に、ほかの PCI デバイスもホストブリッジを介してシステムメモリーにアクセスできます。このアーキテクチャーの利点は、このアーキテクチャーによって I/O バスとプロセッサのホストバスが分離されることです。

PCI ホストブリッジによって、CPU と周辺入出力デバイスの間のデータアクセスマッピングも提供されます。ブリッジは、すべての周辺デバイスをホストアドレスドメインにマッピングして、プロセッサがプログラム式入出力経由でデバイスにアクセスできるようにします。ローカルバス側では、PCI ホストブリッジはシステムメモリーを PCI アドレスドメインにマッピングして、PCI デバイスがバスマスターとしてホストメモリーにアクセスできるようにします。図 A-3 は、2 つのアドレスドメインを示しています。

PCI アドレスドメインは、構成、メモリー、および I/O 空間という 3 つの個別のアドレス空間で構成されています。

構成空間は地理的に定義されます。周辺デバイスの位置は、PCI バスブリッジの相互に接続されたツリー内のその物理的な位置によって決定されます。デバイスは、そのバス番号とデバイス (スロット) 番号によって検出されます。各周辺デバイスには、その PCI 構成空間に一連の十分に定義された構成レジスタが含まれています。レジスタは、デバイスを識別するためだけでなく、構成フレームワークにデバイス構成情報を提供するためにも使用されます。たとえば、デバイスがデータアクセスに応答するためには、デバイス構成空間の基底アドレスレジスタをマッピングする必要があります。

構成サイクルを生成するための方法はホストに依存しています。x86 マシンでは、特殊な I/O ポートが使用されます。ほかのプラットフォームでは、ホストアドレスドメイン内の PCI ホストブリッジに応じて、PCI 構成空間を特定のアドレス位置にメモリーマッピングできます。デバイス構成レジスタにプロセッサがアクセスすると、要求が PCI ホストブリッジにルーティングされます。次に、ブリッジは、そのアクセスをバスの適切な構成サイクルに変換します。

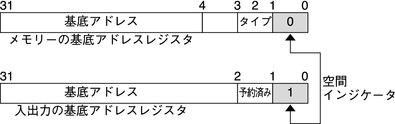

PCI 構成空間は、デバイスごとに最大 6 つの 32 ビット基底アドレスレジスタで構成されています。これらのレジスタは、サイズとデータ型の両方の情報を提供します。システムファームウェアは、PCI アドレスドメインの基底アドレスをこれらのレジスタに割り当てます。

各アドレス指定可能領域には、メモリーまたは I/O 空間を使用できます。基底アドレスレジスタのビット 0 に含まれる値によってタイプが識別されます。ビット 0 にある 0 の値はメモリー空間を示し、1 の値は I/O 空間を示します。次の図は、2 つの基底アドレスレジスタを示しています。1 つはメモリータイプ用で、もう 1 つは入出力タイプ用です。

PCI は、メモリー空間について 32 ビットと 64 ビットの両方のアドレスをサポートしています。システムファームウェアは、PCI アドレスドメインのメモリー空間の領域を PCI 周辺デバイスに割り当てます。領域の基底アドレスは、デバイスの PCI 構成空間の基底アドレスレジスタに格納されます。各領域のサイズは 2 のべき乗にする必要があり、割り当てられる基底アドレスは領域のサイズと等しい境界で割り当てる必要があります。メモリー空間のデバイスアドレスはホストアドレスドメインにメモリーマッピングされるため、デバイスへのデータアクセスはプロセッサのネイティブのロード命令またはストア命令によって実行できます。

PCI は、32 ビット I/O 空間をサポートしています。I/O 空間にアクセスする方法はプラットフォームによって異なります。Intel プロセッサファミリなどの特殊な入出力命令を持つプロセッサは、in および out 命令を使って I/O 空間にアクセスします。特殊な入出力命令を持たないマシンは、ホストアドレスドメインの PCI ホストブリッジに応じてアドレス位置にマッピングします。プロセッサがメモリーマッピングされたアドレスにアクセスすると、入出力要求が PCI ホストブリッジに送られ、次にアドレスが入出力サイクルに変換されて PCI バスに配置されます。メモリーマッピングされた入出力は、プロセッサのネイティブのロード/ストア命令によって実行されます。

ハードウェア構成ファイルは、PCI ローカルバスデバイスには必要ないはずです。ただし、場合によっては、PCI デバイスのドライバはハードウェア構成ファイルを使用してドライバの固有情報を増やす必要があります。詳細は、driver.conf(4)およびpci(4)のマニュアルページを参照してください。

標準の PCI バスは、PCI Express に発展しています。PCI Express は、デスクトップ、モバイル、ワークステーション、サーバー、埋め込み型コンピューティング/通信プラットフォームなどのアプリケーションで周辺デバイスを接続するための、次世代の高性能 I/O バスです。

PCI Express ではバスパフォーマンスが向上し、全体的なシステムコストが減少し、コンピュータ設計の新しい発展を活用しています。PCI Express では、2 つのデバイス間の通信にシリアルのポイントツーポイント型相互接続を使用します。スイッチの使用により、ユーザーはシステム内の多数のデバイスを一緒に接続できます。シリアルの相互接続では、デバイスパッケージあたりのピンが少なくなるので、コストが減少し、パフォーマンスが高度にスケーラブルになります。

PCI Express バスには、次の技術に対応する機能が組み込まれています。

QoS (Quality of Service)

ホットプラグによる取り付けとホットスワップ

詳細な電源管理

RAS (信頼性、可用性、保守性)

向上したエラー処理

MSI 割り込み

2 つのデバイスを一緒に接続する PCI Express の相互接続は、リンクと呼ばれます。リンクでは、x1、x2、x4、x8、x12、x16、または x32 の双方向のシグナルペアを使用できます。これらのシグナルは、レーンと呼ばれます。各レーンの帯域幅 (x1) は、全二重モードで 500M バイト/秒です。PCI-X と PCI Express のハードウェア接続は異なりますが、2 つのバスはドライバの作成者の観点からは同じです。PCI-X は共有バスです。たとえば、バス上のすべてのデバイスが 1 つのセットのデータラインとシグナルラインを共有します。PCI-Express はスイッチバスであり、デバイスとシステムバスの間で帯域幅を使用するときの効率を向上させることができます。

PCI Express の詳細については、Web サイト http://www.pcisig.com/home を参照してください。

通常の SBus システムは、マザーボード (CPU と SBus インタフェースロジックを含む)、マザーボード自体にあるいくつかの SBus デバイス、およびいくつかの SBus 拡張スロットで構成されています。SBus は、適切なバスブリッジを介して、ほかのタイプのバスに接続することもできます。

SBus は地理的にアドレス指定されます。各 SBus スロットは、システム内の固定した物理アドレスに存在します。SBus カードは、差し込むスロットによってアドレスが異なります。SBus デバイスを新しいスロットに移動すると、システムはこのデバイスを新しいデバイスと見なします。

SBus では、ポーリング方式の割り込みを使用します。SBus デバイスが割り込みを行っても、システムは、いくつかあるデバイスのどれかが割り込みを実行した可能性があることしか認識できません。システムの割り込みハンドラは、各デバイスのドライバに、そのデバイスが割り込みを行ったかどうか問い合わせる必要があります。

次の表は、Sun UltraSPARC 2 コンピュータの物理アドレス空間のレイアウトを示しています。UltraSPARC 2 モデルの物理アドレスは、41 ビットで構成されています。41 ビットの物理アドレス空間はさらに、PA(40:33) によって識別される複数の 33 ビットアドレス空間に細分化されます。

表 A-1 Ultra 2 のデバイス物理空間

|

SBus には、『SBus Specification』で説明されているように、32 のアドレスビットがあります。次の表で、Ultra 2 でアドレスビットを使用する方法について説明します。

表 A-2 Ultra 2 の SBus のアドレスビット

|

このアドレス指定方式により、表 A-1 に示す Ultra 2 アドレスが生成されます。ほかの実装では、異なる数のアドレスビットを使用することがあります。

Ultra 2 には 7 つの SBus スロットがあり、そのうちの 4 つは物理的です。スロット 0 - 3 は、SBus カードで使用できます。スロット 4 - 12 は、予約されています。これらのスロットは、次のように使用します。

スロット D、E、および F は、実際の物理スロットではありませんが、オンボードのダイレクトメモリーアクセス (DMA)、SCSI、Ethernet、およびオーディオコントローラを参照します。便宜上、これらのクラスのデバイスは、スロット D、E、および F に差し込まれているものと見なされます。

注 - 一部の SBus スロットは、スレーブのみのスロットです。DMA 機能が必要なドライバでは、ddi_slaveonly(9F) を使用して、デバイスが DMA 対応のスロットに入っているかどうかを判定するべきです。この関数の例については、「attach() エントリポイント」を参照してください。

ハードウェア構成ファイルは通常、SBus デバイスには必要ありません。ただし、場合によっては、SBus デバイスのドライバは、ハードウェア構成ファイルを使用して、SBus カードが提供する情報を増やす必要があります。詳細は、driver.conf(4)およびsbus(4)のマニュアルページを参照してください。