| ナビゲーションリンクをスキップ | |

| 印刷ビューの終了 | |

|

デバイスドライバの記述 Oracle Solaris 11.1 Information Library (日本語) |

| ナビゲーションリンクをスキップ | |

| 印刷ビューの終了 | |

|

デバイスドライバの記述 Oracle Solaris 11.1 Information Library (日本語) |

パート I Oracle Solaris プラットフォーム用デバイスドライバの設計

2. Oracle Solaris カーネルとデバイスツリー

22. ドライバのコンパイル、ロード、パッケージ化、およびテスト

23. デバイスドライバのデバッグ、テスト、およびチューニング

データ型に割り当ての制限はありません。ただし、割り当てが正しくないデータ転送を x86 プロセッサで適正に処理するには、追加のメモリーサイクルが必要になることがあります。

注 - カーネルでは浮動小数点演算はサポートされていないため、ドライバでこの演算を実行しないでください。

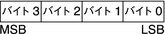

x86 プロセッサでは、リトルエンディアンのバイト順序を使用します。整数の最下位バイト (LSB) は、その整数の一番低いアドレスに格納されます。最上位バイトは、このプロセッサのデータ項目の一番高いアドレスに格納されます。たとえば、バイト 7 は 64 ビットプロセッサの最上位バイトです。

Intel Corporation も AMD も、x86 ファミリのプロセッサに関する書籍を多数出版しています。http://www.intel.com および http://www.amd.com/ を参照してください。