6.2 AMD64 ABI Features

64-bit applications are described by using Executable and Linking Format (ELF64), which allows large applications and large address spaces to be described completely.

-

The AMD ABI allows all 64-bit instructions and 64-bit registers to be used to their full effect. Many of the new instructions are straightforward extensions of the existing i386 instruction set. There are now sixteen general purpose registers.

- Seven general purpose registers (%rdi, %rsi, %rdx, %rcx, %r8, %r9, and %rax) have a well-defined role in the function call sequence which now passes arguments in registers.

- Two registers are used for stack management (%rsp and %rbp). The %rbp register can also be used as a general purpose register.

- Two registers are temporaries (%r10 and %r11).

- Seven registers are callee-saved (%r12, %r13, %r14, %r15, %rbx, %rsp, %rbp).

-

The basic function calling convention is different for the AMD ABI. Arguments are placed in registers. For simple integer arguments, the first arguments are placed in the %rdi, %rsi, %rdx, %rcx, %r8, and %r9 registers in order. Floating-point arguments are placed from %xmm0 to %xmm7 registers.

-

The layout of the stack is slightly different for AMD. In particular, the stack is always aligned on a 16-byte boundary immediately preceding the call instruction. AMD64 has special area on stack called red zone. This is 128-byte area beyond the location pointed to by %rsp is considered to be reserved and shall not be modified by signal or interrupt handlers.

-

Instruction sizes are still 32-bit. Address constant generation therefore takes more instructions. The call instruction can no longer be used to branch anywhere in the address space, since it can only reach within plus or minus 2 gigabytes of %rip.

-

Integer multiply and divide functions are now implemented completely in hardware.

-

Structure passing and return are accomplished differently. Small data structures and some floating point arguments are now passed directly in registers.

-

There are new PC-relative addressing modes that enable more efficient position-independent code to be generated.

-

All data types are now aligned to their size.

-

Many basic derived types are larger. Thus many system call interface data structures are now of different sizes.

-

Two different sets of libraries exist on the system: those for 32-bit i386 applications and those for 64-bit amd64 applications.

-

The AMD ABI substantially enhances floating point capabilities.

- The 64-bit ABI allows all the x87 and MMX instructions that operate on the x87 floating point registers (%fpr0 through %fpr7 and %mm0 through %mm7) to be used.

- Additionally, the full set of SSE and SSE2 instructions that operate on the 128-bit XMM registers (%xmm0 through %xmm15) can be used.

- Also the full set of AVX instructions that operate on the 256-bit YMM registers can be used and support for AVX instructions is optional.

Following is a list of the AMD ABI features.

For more information about amd64 ABI see, System V Application Binary Interface, AMD64 Architecture Processor Supplement.

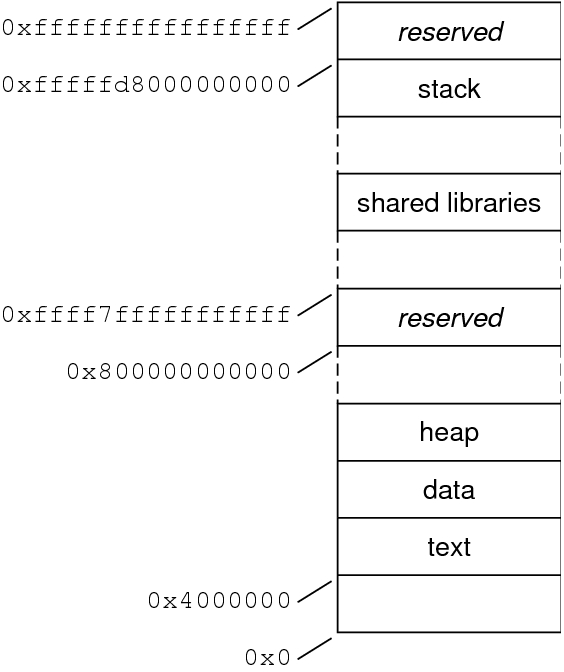

6.2.1 Address Space Layout for amd64 Applications

For 64-bit applications, the layout of the address space is closely related to that of 32-bit applications, though the starting address and addressing limits are radically different. Like SPARC V9, the amd64 stack grows down from the top of the address space, while the heap extends the data segment from the bottom.

The following diagram shows the default address space provided to a 64-bit application. The regions of the address space marked as reserved might not be mapped by applications. These restrictions might be relaxed on future operating systems.

The actual addresses in the figure above describe a particular implementation on a particular system, and are given for illustrative purposes only.