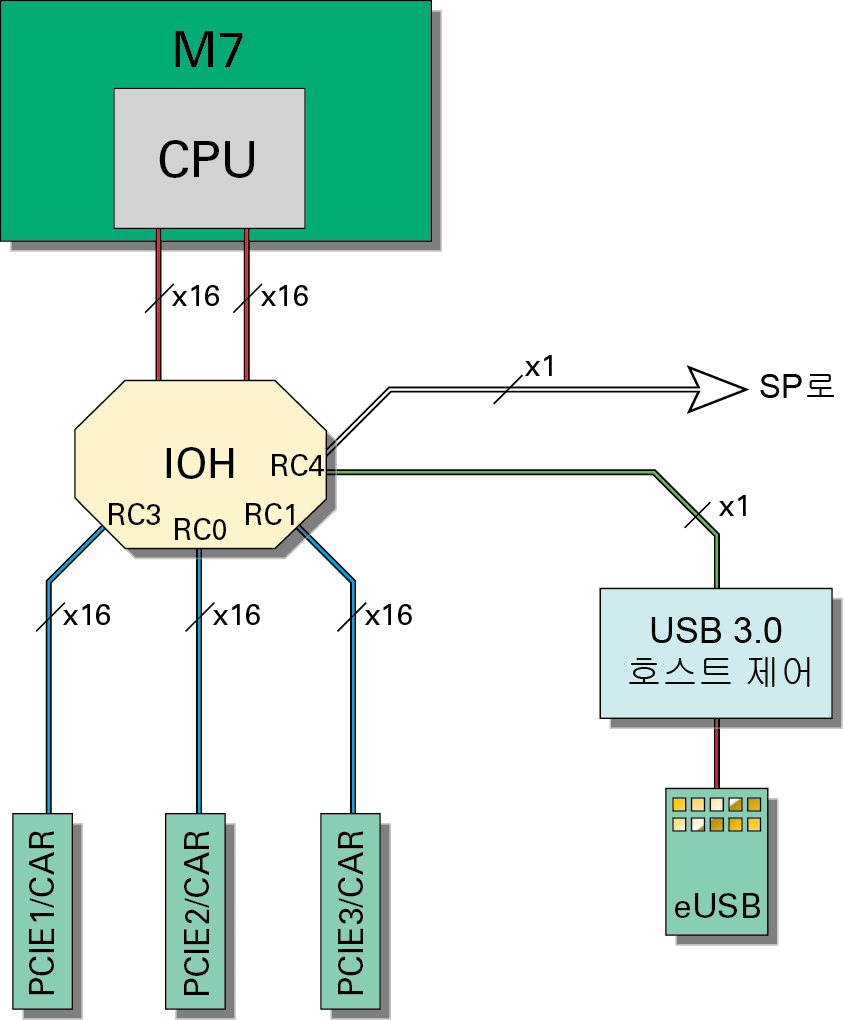

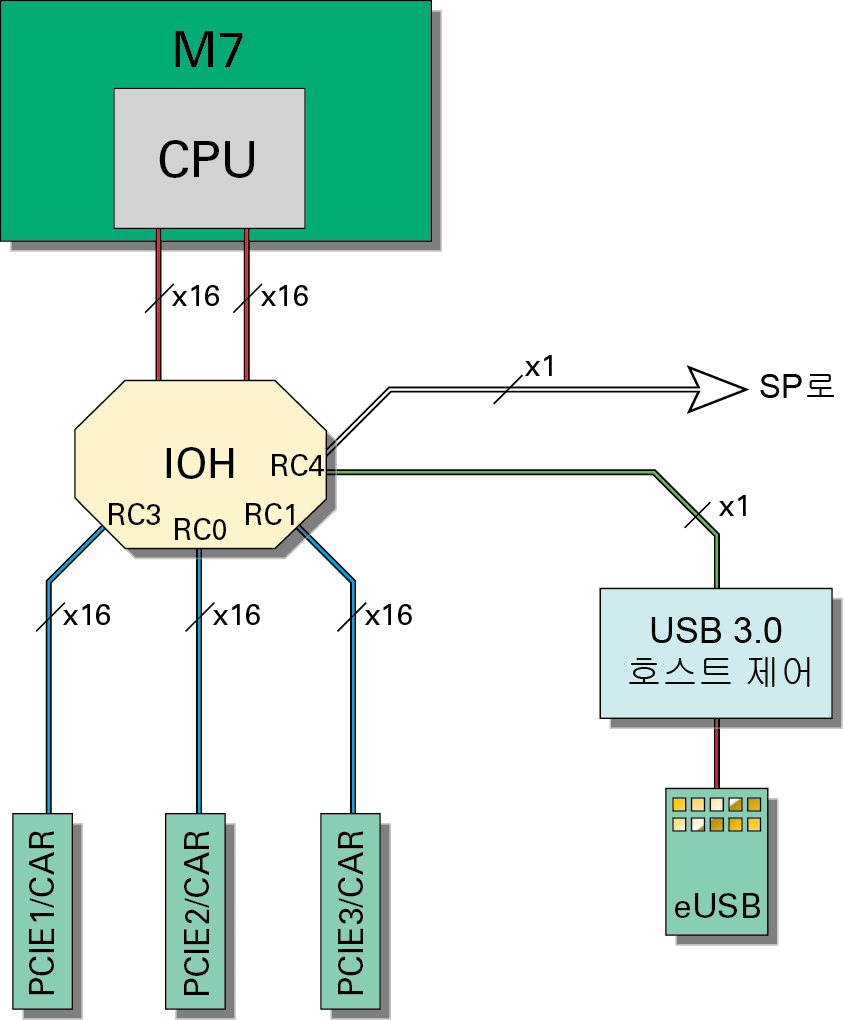

물리적 I/O 구조

이러한 서버의 물리적 I/O 구조가 M 시리즈 서버의 이전 릴리스와 다르게 변경되었습니다. 다른 이름이 사용되고 CPU가 더 이상 PCIe 패브릭을 소유하지 않습니다.

I/O 용어

I/O 구조를 설명하는 데 사용되는 용어가 변경되었습니다.

-

루트 컴플렉스 - PCIe 장치 경로에서 루트 컴플렉스는 항상 첫번째 요소(예: /pci@300)입니다. M 시리즈 서버의 이전 릴리스에서는 CMT 프로세서에 하나 이상의 루트 컴플렉스가 포함되어 있었습니다. 이 기능은 I/O 컨트롤러 칩(IOH)으로 이동되었습니다. 각 서버에는 하나 이상의 I/O 컨트롤러 칩이 있습니다.

-

루트 포트 - 루트 컴플렉스는 하나 이상의 루트 포트를 포함할 수 있습니다. 각 루트 포트는 패브릭 내에서 서로 독립적입니다. 하지만 동일한 루트 컴플렉스 아래의 모든 장치가 해당 패브릭을 공유합니다.

루트 포트는 항상 PCIe 장치 경로의 두번째 용어입니다. 루트 포트는 항상 첫번째부터 pci@1, pci@2 등의 순으로 지정됩니다.

-

PCI 버스 - 논리적 도메인에 루트 컴플렉스를 지정하는 데 사용하는 레이블입니다.

루트 컴플렉스 지정

이 그림은 한 CMIOU에 대한 루트 컴플렉스 지정을 보여줍니다.

각 루트 컴플렉스에는 장치 경로, 서비스 경로 및 버스 이름이 있습니다. 이 표에는 CMIOU0 및 CMIOU1의 이름 지정이 예제로 포함되어 있습니다. 모든 CMIOU 이름 지정 예제는 물리적 I/O 구조를 참조하십시오.

|

|

|

|

|

|

CMIOU0

|

/pci@301/pci@1

|

/SYS/CMIOU0/PCIE3

|

pci_1

|

일반적으로 부트 디스크 어댑터에 사용됩니다.

|

|

/pci@300/pci@1

|

/SYS/CMIOU0/PCIE2

|

pci_0

|

|

|

/pci@303/pci@1

|

/SYS/CMIOU0/PCIE1

|

pci_3

|

|

|

CMIOU1

|

/pci@306/pci@1

|

/SYS/CMIOU1/PCIE3

|

pci_6

|

일반적으로 네트워크 어댑터에 사용됩니다.

|

|

/pci@305/pci@1

|

/SYS/CMIOU1/PCIE2

|

pci_5

|

|

|

/pci@308/pci@1

|

/SYS/CMIOU1/PCIE1

|

pci_8

|

|

|

I/O 구조 레이아웃

이 다이어그램은 PDomain이 하나인 SPARC M7-8 서버에 대한 I/O 구조 레이아웃을 보여줍니다. SPARC M7-16 서버의 경우 이 다이어그램에 I/O 구조의 1/2이 표시됩니다. PDomain이 두 개인 SPARC M7-8 서버의 경우 이 다이어그램에 두 정적 도메인 모두에 대한 I/O 구조 레이아웃이 표시됩니다.

주 -

이 다이어그램은 SP와 CMIOU4 및 CMIOU5 사이의 연결을 보여줍니다. 선이 있지만 연결은 PDomain이 하나인 SPARC M7-8 서버에서 활성화되지 않고, PDomain이 두 개인 SPARC M7-8 서버 및 SPARC M7-16 서버에서 활성화됩니다.

I/O 구성 요소 예제 출력

ldm list-io 명령은 서버의 I/O 장치에 대한 정보를 나열합니다. ldm list-io 출력을 검색하여 설치된 PCIe 장치의 루트 컴플렉스와 루트 포트(출력에서 대괄호 안에 지정됨) 및 슬롯 번호(예를 들어, PCIE2는 CMIOU0의 슬롯 2임)를 확인하고 관리를 위해 논리적 도메인에 루트 컴플렉스를 지정하는 데 사용하는 BUS 이름(예: pci_0)을 확인할 수 있습니다. 이 출력은 알아보기 쉽도록 편집한 것입니다.

# ldm list-io -l

NAME TYPE BUS DOMAIN STATUS

---- ---- --- ------ ------

...

/SYS/CMIOU0/PCIE2 PCIE pci_0 primary EMP

[pci@300/pci@1]

/SYS/CMIOU0/PCIE3 PCIE pci_1 primary OCC

[pci@301/pci@1]

LSI,sas@0/iport@80

LSI,sas@0/iport@v0

/SYS/CMIOU0/PCIE1 PCIE pci_3 primary OCC

[pci@303/pci@1]

network@0

network@0,1

network@0,2

network@0,3

...

#

I/O 구성 요소 관계

다음 표에서는 서버에 설치할 수 있는 각 CMIOU의 루트 컴플렉스 번호, PCIe 슬롯 번호, 루트 컴플렉스 이름, 버스 이름 간의 관계를 나열합니다.

이 표는 서버의 DCU 및 CMIOU 구성 요소에 대해 설명합니다.

|

|

|

|

SPARC M7-8(PDomain 2개)

|

각각 CMIOU 4개가 있는 정적 DCU 두 개

|

|

|

SPARC M7-8(PDomain 1개)

|

CMIOU 8개가 있는 정적 DCU 한 개

|

CMIOU0–7

|

|

SPARC M7-16

|

각각 CMIOU 4개가 있는 동적 DCU 4개

|

-

CMIOU0–3

-

CMIOU4–7

-

CMIOU8–11

-

CMIOU12–15

|

|

표 1 CMIOU0에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@300

|

pci_0

|

|

1

|

PCIE3

|

pci@301

|

pci_1

|

|

3

|

PCIE1

|

pci@303

|

pci_3

|

|

4

|

해당 없음

|

pci@304

|

pci_4

|

|

표 2 CMIOU1에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIe2

|

pci@305

|

pci_5

|

|

1

|

PCIE3

|

pci@306

|

pci_6

|

|

3

|

PCIE1

|

pci@308

|

pci_8

|

|

4

|

해당 없음

|

pci@309

|

pci_9

|

|

표 3 CMIOU2에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@30a

|

pci_10

|

|

1

|

PCIE3

|

pci@30b

|

pci_11

|

|

3

|

PCIE1

|

pci@30d

|

pci_13

|

|

4

|

해당 없음

|

pci@30e

|

pci_14

|

|

표 4 CMIOU3에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@30f

|

pci_15

|

|

1

|

PCIE3

|

pci@310

|

pci_16

|

|

3

|

PCIE1

|

pci@312

|

pci_18

|

|

4

|

N/A

|

pci@313

|

pci_19

|

|

표 5 CMIOU4에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@314

|

pci_20

|

|

1

|

PCIE3

|

pci@315

|

pci_21

|

|

3

|

PCIE1

|

pci@317

|

pci_23

|

|

4

|

해당 없음

|

pci@318

|

pci_24

|

|

표 6 CMIOU5에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@319

|

pci_25

|

|

1

|

PCIE3

|

pci@31a

|

pci_26

|

|

3

|

PCIE1

|

pci@31c

|

pci_28

|

|

4

|

해당 없음

|

pci@31d

|

pci_29

|

|

표 7 CMIOU6에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@31e

|

pci_30

|

|

1

|

PCIE3

|

pci@31f

|

pci_31

|

|

3

|

PCIE1

|

pci@321

|

pci_33

|

|

4

|

해당 없음

|

pci@322

|

pci_34

|

|

표 8 CMIOU7에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@323

|

pci_35

|

|

1

|

PCIE3

|

pci@324

|

pci_36

|

|

3

|

PCIE1

|

pci@326

|

pci_38

|

|

4

|

해당 없음

|

pci@327

|

pci_39

|

|

표 9 CMIOU8에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@328

|

pci_40

|

|

1

|

PCIE3

|

pci@329

|

pci_41

|

|

3

|

PCIE1

|

pci@32b

|

pci_43

|

|

4

|

해당 없음

|

pci@32c

|

pci_44

|

|

표 10 CMIOU9에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@32d

|

pci_45

|

|

1

|

PCIE3

|

pci@32e

|

pci_46

|

|

3

|

PCIE1

|

pci@330

|

pci_48

|

|

4

|

해당 없음

|

pci@331

|

pci_49

|

|

표 11 CMIOU10에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@332

|

pci_50

|

|

1

|

PCIE3

|

pci@333

|

pci_51

|

|

3

|

PCIE1

|

pci@335

|

pci_53

|

|

4

|

해당 없음

|

pci@336

|

pci_54

|

|

표 12 CMIOU11에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@337

|

pci_55

|

|

1

|

PCIE3

|

pci@338

|

pci_56

|

|

3

|

PCIE1

|

pci@33a

|

pci_58

|

|

4

|

해당 없음

|

pci@33b

|

pci_59

|

|

표 13 CMIOU12에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@33c

|

pci_60

|

|

1

|

PCIE3

|

pci@33d

|

pci_61

|

|

3

|

PCIE1

|

pci@33f

|

pci_63

|

|

4

|

해당 없음

|

pci@340

|

pci_64

|

|

표 14 CMIOU13에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@341

|

pci_65

|

|

1

|

PCIE3

|

pci@342

|

pci_66

|

|

3

|

PCIE1

|

pci@344

|

pci_68

|

|

4

|

해당 없음

|

pci@345

|

pci_69

|

|

표 15 CMIOU14에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@346

|

pci_70

|

|

1

|

PCIE3

|

pci@347

|

pci_71

|

|

3

|

PCIE1

|

pci@349

|

pci_73

|

|

4

|

해당 없음

|

pci@34a

|

pci_74

|

|

표 16 CMIOU15에 대한 I/O 구성 요소 이름 지정

|

|

|

|

|

0

|

PCIE2

|

pci@34b

|

pci_75

|

|

1

|

PCIE3

|

pci@34c

|

pci_76

|

|

3

|

PCIE1

|

pci@34e

|

pci_78

|

|

4

|

해당 없음

|

pci@34f

|

pci_79

|

|