偽共有の検出

チュートリアルのこのパートは、「L1 データキャッシュミス」dcm カウンタが正確であるシステムのみが対象です。そのようなシステムには SPARC-T4、SPARC-T5、SPARC-M5、SPARC-M6 などが含まれます。正確な dcm カウンタを備えていないシステムで記録された実験は、このセクションで使用できません。

この手順では、フィルタリングとともに「インデックスオブジェクト」ビューおよび「メモリーオブジェクト」ビューを使用する方法を示します。

正確なメモリー関連カウンタを備えたシステムで実験を作成すると、マシンモデルが実験に記録されます。マシンモデルは、そのマシンのメモリーサブシステム内のさまざまなコンポーネントへのアドレスのマッピングを表します。パフォーマンスアナライザまたは er_print で実験をロードすると、マシンモデルが自動的にロードされます。

このチュートリアルのスクリーンショットで使用する実験は SPARC T5 システムで記録されたものであり、そのマシン用の t5 マシンモデルが自動的に実験とともにロードされます。マシンモデルはインデックスオブジェクトおよびメモリーオブジェクトのデータビューを追加します。

-

「関数」ビューに移動して computeB() を選択し、右クリックして「フィルタの追加: 選択した関数を含むスタックのみを含める」を選択します。

フィルタリングによって、computeB() 関数のパフォーマンスと、その関数で発生するプロファイルイベントに焦点を当てることができます。

-

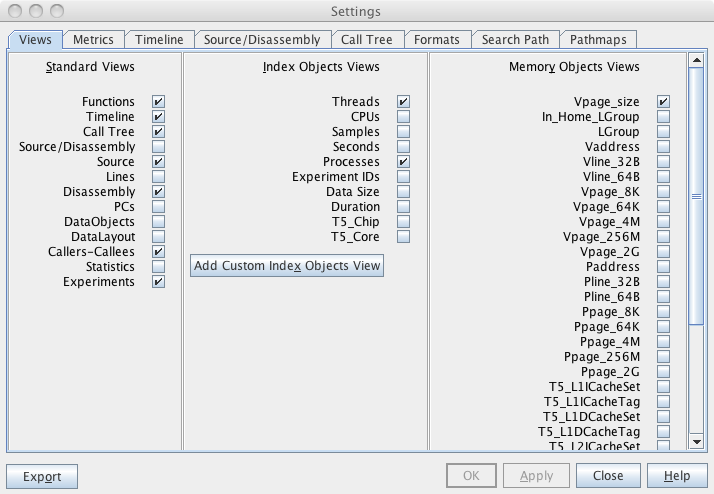

ツールバーの「設定」ボタンをクリック、または「ツール」>「設定」を選択して「設定」ダイアログを開き、そのダイアログで「ビュー」タブを選択します。

右側のパネルには「メモリーオブジェクトビュー」というラベルが付いており、SPARC T5 マシンのメモリーサブシステム構造を表すデータビューの長いリストを示します。

-

「Vaddress」および「Vline_32B」のチェックボックスを選択して「了解」をクリックします。

-

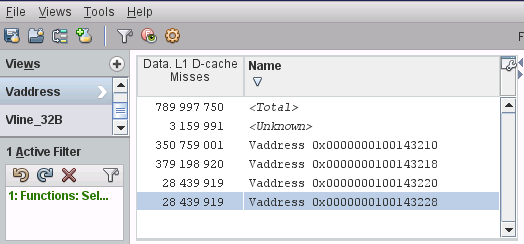

「ビュー」ナビゲーションパネルで「Vaddress」ビューを選択します。

この実験では、4 つの異なるアドレスでキャッシュミスが発生していることがわかります。

-

アドレスのうちの 1 つを選択し、右クリックして「フィルタの追加: 選択した項目を含むイベントのみを含める」を選択します。

-

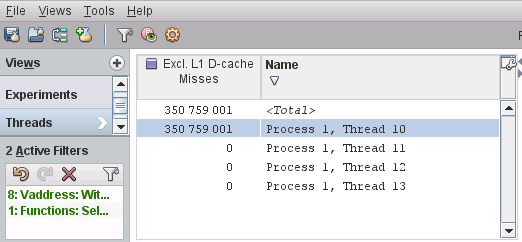

「スレッド」ビューを選択します。

前のスクリーンショットでわかるように、そのアドレスでキャッシュミスが発生しているスレッドは 1 つだけです。

-

ビュー内で右クリックし、コンテキストメニューから「フィルタアクションを元に戻す」を選択して、アドレスフィルタを削除します。

または、「アクティブなフィルタ」パネル内の「フィルタアクションを元に戻す」ボタンを使用すると、フィルタを削除できます。

-

「Vaddress」ビューに戻り、ほかのアドレスを選択してフィルタを適用し、関連するスレッドを「Threads」ビューでチェックします。

このようにして、フィルタを適用および適用解除する、また「Vaddress」ビューと「Threads」ビューを切り替えることによって、4 つのスレッドと 4 つのアドレスの間に 1 対 1 の関係があることを確認できます。つまり、4 つのスレッドはアドレスを共有しません。

-

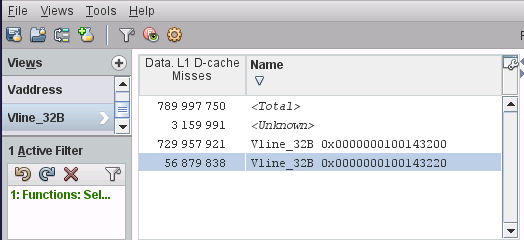

「ビュー」ナビゲーションパネルで「Vline_32B」ビューを選択します。

「アクティブなフィルタ」パネルで、関数 computerB() のフィルタのみがアクティブであることを確認します。フィルタは「関数: 選択した関数」と表示されます。この時点で、どのアドレスフィルタもアクティブではありません。

2 つの 32 バイトキャッシュ行で 4 つのスレッドのキャッシュミスが発生していること、また 4 つのスレッドそれぞれのアドレスを確認できます。4 つのスレッドがアドレスを共有しないことは以前に確認しましたが、ここでは 4 つのスレッドがキャッシュ行を共有することを確認できます。

偽共有は診断が非常に難しい問題であり、SPARC T5 チップでは、Oracle Solaris Studio パフォーマンスアナライザを使用することでその診断が可能になります。