Arquitectura física de E/S

La arquitectura física de E/S de estos servidores ha cambiado de las versiones anteriores de los servidores serie M. Se usan diferentes nombres y la CPU ya no es la propietaria del tejido PCIe.

Terminología de E/S

Estos son los cambios de los términos que se usan para describir la arquitectura de E/S.

-

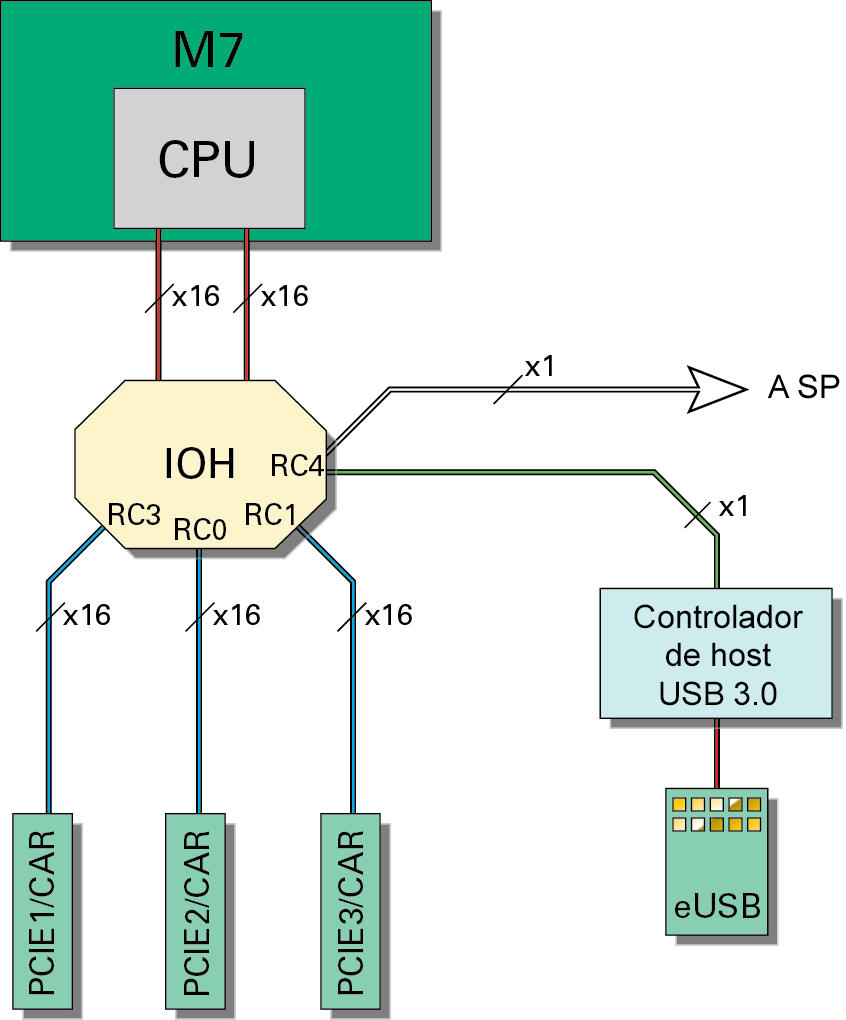

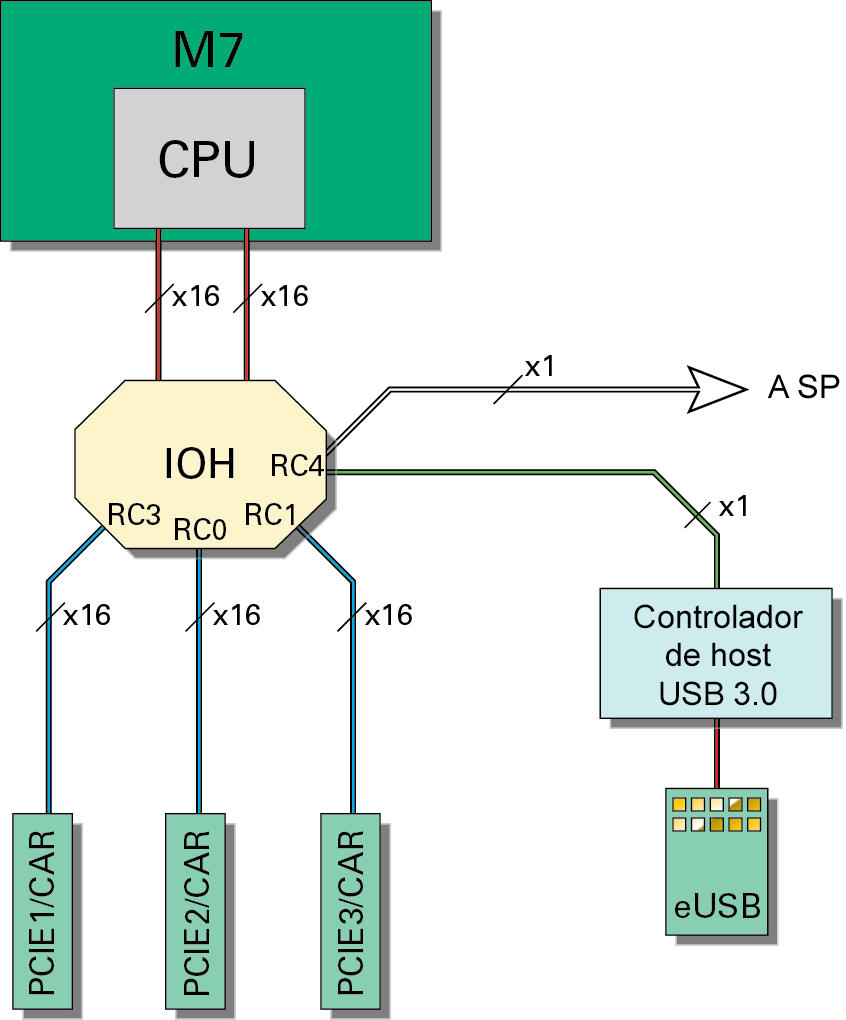

Complejo raíz: en una ruta de dispositivo PCIe, el complejo raíz es siempre el primer elemento (por ejemplo, /pci@300). En versiones anteriores de los servidores serie M, los procesadores CMT contenían uno o más complejos raíz. Esta funcionalidad se movió al chip del controlador de E/S (IOH). Cada servidor tiene uno o más chips de controlador de E/S.

-

Puerto raíz: un complejo raíz puede tener uno o más puertos raíz. Cada puerto raíz es independiente del otro en ese tejido. Sin embargo, cualquier dispositivo dentro del mismo complejo raíz comparte ese tejido.

El puerto raíz es siempre el segundo término de una ruta de dispositivo PCIe. El primer puerto raíz siempre será pci@1, el segundo será pci@2, etc.

-

Bus de PCI: esta es la etiqueta que usa para asignar un complejo raíz a un dominio lógico.

Asignaciones de complejo raíz

En esta figura se muestran las asignaciones de complejos raíz para una CMIOU.

Cada complejo raíz tiene una ruta de dispositivo, una ruta de servicio y un nombre de bus. Esta tabla incluye los nombres para CMIOU0 y CMIOU1 a modo de ejemplo. Para ver ejemplos de nombres para todas las CMIOU, consulte Arquitectura física de E/S.

|

|

|

|

|

|

CMIOU0

|

/pci@301/pci@1

|

/SYS/CMIOU0/PCIE3

|

pci_1

|

Por lo general, se utiliza para el adaptador de disco de inicio.

|

|

/pci@300/pci@1

|

/SYS/CMIOU0/PCIE2

|

pci_0

|

|

|

/pci@303/pci@1

|

/SYS/CMIOU0/PCIE1

|

pci_3

|

|

|

CMIOU1

|

/pci@306/pci@1

|

/SYS/CMIOU1/PCIE3

|

pci_6

|

Por lo general, se utiliza para el adaptador de red.

|

|

/pci@305/pci@1

|

/SYS/CMIOU1/PCIE2

|

pci_5

|

|

|

/pci@308/pci@1

|

/SYS/CMIOU1/PCIE1

|

pci_8

|

|

|

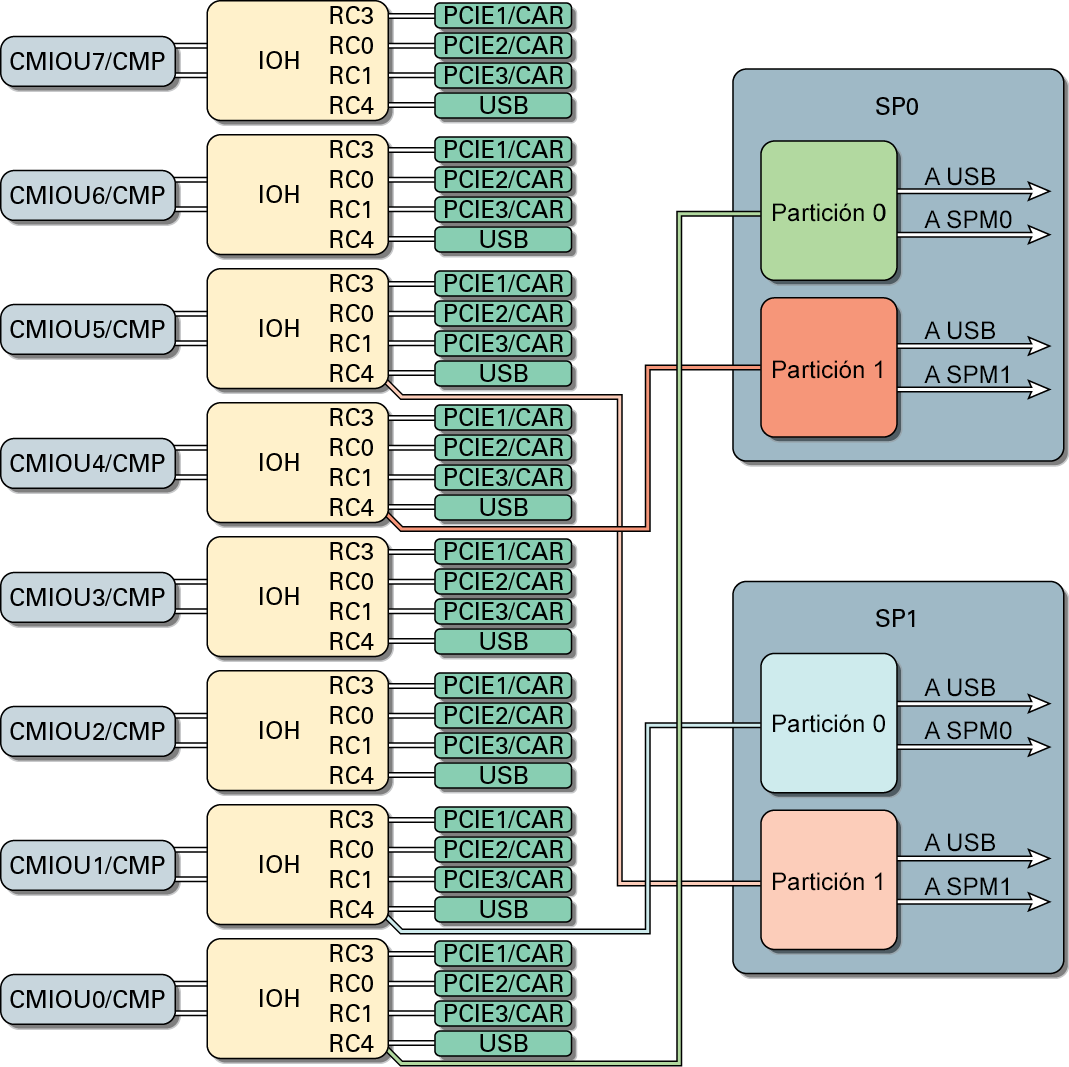

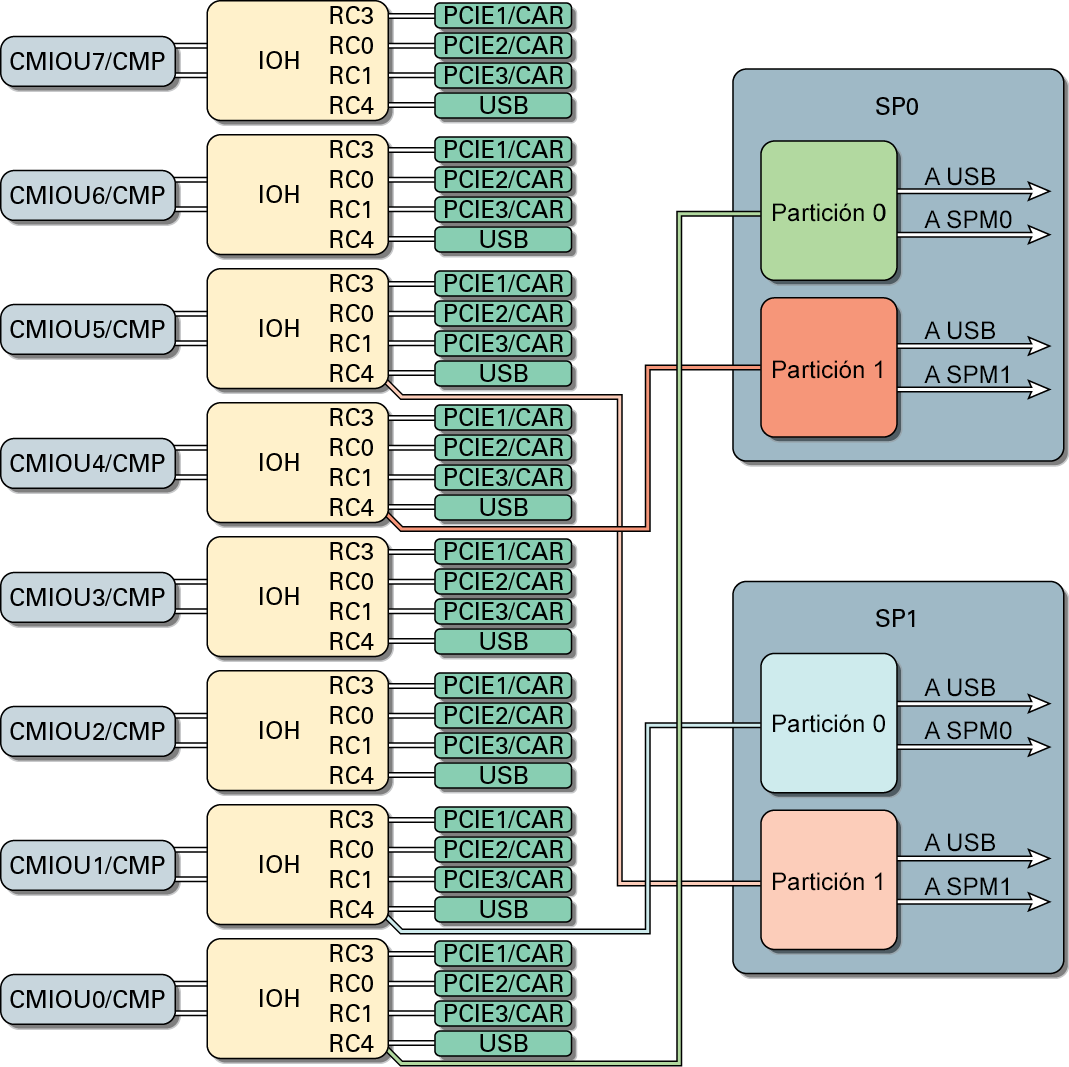

Diseño de arquitectura de E/S

Este diagrama muestra el diseño de arquitectura de E/S para el servidor SPARC M7-8 con un PDomain. Para el servidor SPARC M7-16, el diagrama representa una mitad de la arquitectura de E/S. Para el servidor SPARC M7-8 con dos PDomains, el diagrama representa el diseño de arquitectura de E/S para ambos dominios estáticos.

Notas -

En este diagrama, se muestran conexiones entre los SP, y CMIOU4 y CMIOU5. Si bien los cables están presentes, las conexiones no están activas en el servidor SPARC M7-8 con un PDomain. Están activas en el servidor SPARC M7-8 con dos PDomains y en los servidores SPARC M7-16.

Salida de ejemplo de componente de E/S

El comando ldm list-io muestra información acerca de los dispositivos de E/S en el servidor. Mediante la búsqueda de la salida ldm list-io, puede determinar el complejo raíz y el puerto raíz de un dispositivo PCIe instalado (que se muestra entre corchetes en la salida), el número de ranura (por ejemplo, PCIE2 es la ranura 2 en CMIOU0) y, para fines administrativos, el nombre de BUS (por ejemplo, pci_0) que usa para asignar un complejo raíz a un dominio lógico. Se editó esta salida para una mayor claridad.

# ldm list-io -l

NAME TYPE BUS DOMAIN STATUS

---- ---- --- ------ ------

...

/SYS/CMIOU0/PCIE2 PCIE pci_0 primary EMP

[pci@300/pci@1]

/SYS/CMIOU0/PCIE3 PCIE pci_1 primary OCC

[pci@301/pci@1]

LSI,sas@0/iport@80

LSI,sas@0/iport@v0

/SYS/CMIOU0/PCIE1 PCIE pci_3 primary OCC

[pci@303/pci@1]

network@0

network@0,1

network@0,2

network@0,3

...

#

Relaciones de componentes de E/S

Estas tablas muestran las relaciones entre los números de los complejos raíz, los números de las ranuras de PCIe, los nombres de complejos raíz y los nombres de bus en cada CMIOU que instala en los servidores.

En esta tabla, se explican los componentes de CMIOU y DCU de los servidores.

|

|

|

|

SPARC M7-8 (dos PDomains)

|

Dos estáticos con cuatro CMIOU cada uno

|

|

|

SPARC M7-8 (un PDomain)

|

Uno estático con ocho CMIOU

|

CMIOU0–7

|

|

SPARC M7-16

|

Cuatro dinámicos con cuatro CMIOU cada uno

|

-

CMIOU0–3

-

CMIOU4–7

-

CMIOU8–11

-

CMIOU12–15

|

|

Tabla 1 Asignación de nombres de componentes de E/S para CMIOU0

|

|

|

|

|

0

|

PCIE2

|

pci@300

|

pci_0

|

|

1

|

PCIE3

|

pci@301

|

pci_1

|

|

3

|

PCIE1

|

pci@303

|

pci_3

|

|

4

|

N/D

|

pci@304

|

pci_4

|

|

Tabla 2 Asignación de nombres de componentes de E/S para CMIOU1

|

|

|

|

|

0

|

PCIe2

|

pci@305

|

pci_5

|

|

1

|

PCIE3

|

pci@306

|

pci_6

|

|

3

|

PCIE1

|

pci@308

|

pci_8

|

|

4

|

N/D

|

pci@309

|

pci_9

|

|

Tabla 3 Asignación de nombres de componentes de E/S para CMIOU2

|

|

|

|

|

0

|

PCIE2

|

pci@30a

|

pci_10

|

|

1

|

PCIE3

|

pci@30b

|

pci_11

|

|

3

|

PCIE1

|

pci@30d

|

pci_13

|

|

4

|

N/D

|

pci@30e

|

pci_14

|

|

Tabla 4 Asignación de nombres de componentes de E/S para CMIOU3

|

|

|

|

|

0

|

PCIE2

|

pci@30f

|

pci_15

|

|

1

|

PCIE3

|

pci@310

|

pci_16

|

|

3

|

PCIE1

|

pci@312

|

pci_18

|

|

4

|

N/A

|

pci@313

|

pci_19

|

|

Tabla 5 Asignación de nombres de componentes de E/S para CMIOU4

|

|

|

|

|

0

|

PCIE2

|

pci@314

|

pci_20

|

|

1

|

PCIE3

|

pci@315

|

pci_21

|

|

3

|

PCIE1

|

pci@317

|

pci_23

|

|

4

|

N/D

|

pci@318

|

pci_24

|

|

Tabla 6 Asignación de nombres de componentes de E/S para CMIOU5

|

|

|

|

|

0

|

PCIE2

|

pci@319

|

pci_25

|

|

1

|

PCIE3

|

pci@31a

|

pci_26

|

|

3

|

PCIE1

|

pci@31c

|

pci_28

|

|

4

|

N/D

|

pci@31d

|

pci_29

|

|

Tabla 7 Asignación de nombres de componentes de E/S para CMIOU6

|

|

|

|

|

0

|

PCIE2

|

pci@31e

|

pci_30

|

|

1

|

PCIE3

|

pci@31f

|

pci_31

|

|

3

|

PCIE1

|

pci@321

|

pci_33

|

|

4

|

N/D

|

pci@322

|

pci_34

|

|

Tabla 8 Asignación de nombres de componentes de E/S para CMIOU7

|

|

|

|

|

0

|

PCIE2

|

pci@323

|

pci_35

|

|

1

|

PCIE3

|

pci@324

|

pci_36

|

|

3

|

PCIE1

|

pci@326

|

pci_38

|

|

4

|

N/D

|

pci@327

|

pci_39

|

|

Tabla 9 Asignación de nombres de componentes de E/S para CMIOU8

|

|

|

|

|

0

|

PCIE2

|

pci@328

|

pci_40

|

|

1

|

PCIE3

|

pci@329

|

pci_41

|

|

3

|

PCIE1

|

pci@32b

|

pci_43

|

|

4

|

N/D

|

pci@32c

|

pci_44

|

|

Tabla 10 Asignación de nombres de componentes de E/S para CMIOU9

|

|

|

|

|

0

|

PCIE2

|

pci@32d

|

pci_45

|

|

1

|

PCIE3

|

pci@32e

|

pci_46

|

|

3

|

PCIE1

|

pci@330

|

pci_48

|

|

4

|

N/D

|

pci@331

|

pci_49

|

|

Tabla 11 Asignación de nombres de componentes de E/S para CMIOU10

|

|

|

|

|

0

|

PCIE2

|

pci@332

|

pci_50

|

|

1

|

PCIE3

|

pci@333

|

pci_51

|

|

3

|

PCIE1

|

pci@335

|

pci_53

|

|

4

|

N/D

|

pci@336

|

pci_54

|

|

Tabla 12 Asignación de nombres de componentes de E/S para CMIOU11

|

|

|

|

|

0

|

PCIE2

|

pci@337

|

pci_55

|

|

1

|

PCIE3

|

pci@338

|

pci_56

|

|

3

|

PCIE1

|

pci@33a

|

pci_58

|

|

4

|

N/D

|

pci@33b

|

pci_59

|

|

Tabla 13 Asignación de nombres de componentes de E/S para CMIOU12

|

|

|

|

|

0

|

PCIE2

|

pci@33c

|

pci_60

|

|

1

|

PCIE3

|

pci@33d

|

pci_61

|

|

3

|

PCIE1

|

pci@33f

|

pci_63

|

|

4

|

N/D

|

pci@340

|

pci_64

|

|

Tabla 14 Asignación de nombres de componentes de E/S para CMIOU13

|

|

|

|

|

0

|

PCIE2

|

pci@341

|

pci_65

|

|

1

|

PCIE3

|

pci@342

|

pci_66

|

|

3

|

PCIE1

|

pci@344

|

pci_68

|

|

4

|

N/D

|

pci@345

|

pci_69

|

|

Tabla 15 Asignación de nombres de componentes de E/S para CMIOU14

|

|

|

|

|

0

|

PCIE2

|

pci@346

|

pci_70

|

|

1

|

PCIE3

|

pci@347

|

pci_71

|

|

3

|

PCIE1

|

pci@349

|

pci_73

|

|

4

|

N/D

|

pci@34a

|

pci_74

|

|

Tabla 16 Asignación de nombres de componentes de E/S para CMIOU15

|

|

|

|

|

0

|

PCIE2

|

pci@34b

|

pci_75

|

|

1

|

PCIE3

|

pci@34c

|

pci_76

|

|

3

|

PCIE1

|

pci@34e

|

pci_78

|

|

4

|

N/D

|

pci@34f

|

pci_79

|

|