Advanced Rear Transition Module Connectors (Zone 3)

The blade server provides all the I/O connections for rear access through the

Zone 3 ARTM connectors, which support the following:

-

GbE management port

-

Serial port

-

x8 PCIe slot

Zone 3 connector pins are presented from the point of view of the

ATCA blade. The TX means the ATCA blade is the signal source, and

the ARTM is the signal receiver. Similarly, RX means the ATCA blade is

the signal receiver and the ARTM is the signal source.

The “reserved” pins indicate connector pins that are currently reserved for compatibility to

all ARTMs. Do not connect signals to reserved pins. The “no connect” indicates pins

that should not be connected by the blade server.

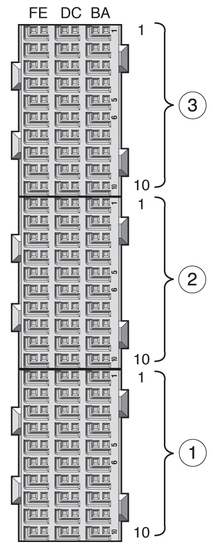

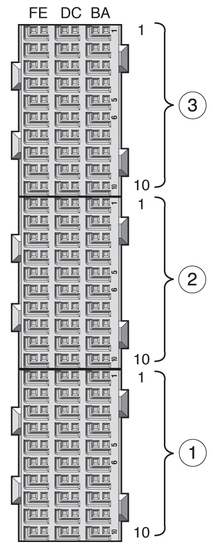

The ARTM Zone 3 connectors are shown in the following figure.

Figure 10 ARTM Connectors (Zone 3)

Figure Legend

1 Zone 3 J33

2 Zone 3 J32

3 Zone 3 J31

For pin assignments of ARTM Zone 3, see the following:

For descriptions of the signals, see Zone 3 Signal Descriptions.

Zone 3 Power Connector Pin Assignments

The connector pin assignments are used for power signals.

|

|

|

|

|

|---|

E |

RTM_PS1_L |

N/C |

Short |

Last |

D |

+12V_RTM |

+12V_RTM |

Long |

First |

C |

I2C_RTMCONN_SCL |

I2C_RTMCONN_SDA |

Medium |

Second |

B |

Logic_GND |

+3.3V_STBY_RTM |

Long |

First |

A |

Logic_GND |

Shelf_GND |

Long |

First |

|

Zone 3 I/O (J31) Connector Pin Assignments

The J31 connector pin assignments are used for I/O RTM signals.

Note - N/U means not used.

|

|

|

|

|

|

|

|---|

1 |

Z3_F1_TX1+ |

Z3_F1_TX1- |

Z3_F1_RX0+ |

Z3_F1_RX0- |

Z3_F1_TX0+ |

Z3_F1_TX0- |

2 |

Z3_F1_RX2+ |

Z3_F1_RX2- |

Z3_F1_TX2+ |

Z3_F1_TX2- |

Z3_F1_RX1+ |

Z3_F1_RX1- |

3 |

Z3_F2_TX0+ |

Z3_F2_TX0- |

Z3_F1_RX3+ |

Z3_F1_RX3- |

Z3_F1_TX3+ |

Z3_F1_TX3- |

4 |

Z3_F2_RX1+ |

Z3_F2_RX1- |

Z3_F2_TX1+ |

Z3_F2_TX1- |

Z3_F2_RX0+ |

Z3_F2_RX0- |

5 |

Z3_F2_TX3+ |

Z3_F2_TX3- |

Z3_F2_RX2+ |

Z3_F2_RX2- |

Z3_F2_TX2+ |

Z3_F2_X2- |

6 |

N/U |

N/U |

N/U |

N/U |

Z3_F2_RX3+ |

Z3_F2_RX3- |

7 |

N/U |

N/U |

N/U |

N/U |

N/U |

N/U |

8 |

N/U |

N/U |

N/U |

N/U |

N/U |

N/U |

9 |

N/U |

N/U |

N/U |

N/U |

N/U |

N/U |

10 |

N/U |

N/U |

N/U |

N/U |

N/U |

N/U |

|

Zone 3 Infrastructure (J32) Connector Pin Assignments

The J32 connector pin assignments are used for infrastructure signals.

Note - N/U means not used, and N/C means not connected.

|

|

|

|

|

|

|

|---|

1 |

XAUI_MDIO |

XAUI_MDC |

N/U |

N/U |

N/U |

N/U |

2 |

N/U |

N/U |

N/U |

N/U |

SER_RJ45_RTS |

SER_RJ45_DTR |

3 |

N/U |

N/U |

N/U |

N/U |

SER_RJ45_TXD |

SER_RJ45_RXD |

4 |

N/U |

N/U |

N/U |

N/U |

SER_RJ45_DSR |

SER_RJ45_CTS |

5 |

N/U |

N/U |

N/U |

N/U |

N/C |

N/C |

6 |

RTM_LAN0_A+ |

RTM_LAN0_A- |

RTM_TXFRMR_VOLTAGE |

RTM_TXFRMR_VOLTAGE |

RTM_LAN0_B+ |

RTM_LAN0_B- |

7 |

RTM_LAN0_C+ |

RTM_LAN0_C- |

RTM_ACT_LED_N |

RTM_LINK_LED_N |

RTM_LAN0_D+ |

RTM_LAN0_D- |

8 |

N/C |

N/C |

N/C |

N/C |

N/C |

N/C |

9 |

N/C |

N/C |

N/C |

N/C |

N/U |

N/U |

10 |

N/U |

N/U |

N/U |

N/U |

N/U |

N/U |

|

Zone 3 PCIe (J33) Connector Pin Assignments

The J33 connector pin assignments are used for PCIe signals.

Note - N/U means not used, and N/C means not connected.

|

|

|

|

|

|

|

|---|

1 |

RTM_TX0+ |

RTM_TX0- |

RTM_RX0+ |

RTM_RX0- |

RTM_CON_REF CLK+ |

RTM CON_REF CLK- |

2 |

RTM_TX1+ |

RTM_TX1- |

RTM_RX1+ |

RTM_RX1- |

TCLKA+ |

TCLKA- |

3 |

RTM_TX2+ |

RTM_TX2- |

RTM_RX2+ |

RTM_RX2- |

TCLKB+ |

TCLKB- |

4 |

RTM_TX3+ |

RTM_TX3- |

RTM_RX3+ |

RTM_RX3- |

TCLKC+ |

TCLKC- |

5 |

RTM_TX4+ |

RTM_TX4- |

RTM_RX4+ |

RTM_RX4- |

TCLKD+ |

TCLKD- |

6 |

RTM_TX5+ |

RTM_TX5- |

RTM_RX5+ |

RTM_RX5- |

N/U |

N/U |

7 |

RTM_TX6+ |

RTM_TX6- |

RTM_RX6+ |

RTM_RX6- |

N/U |

N/U |

8 |

RTM_TX7+ |

RTM_TX7- |

RTM_RX7+ |

RTM_RX7- |

N/U |

FPGA_PRESET_RTM- |

9 |

N/C |

N/C |

N/C |

N/C |

RTM_MMC_L |

PCI_CFG |

10 |

N/U |

N/U |

N/U |

N/U |

GND |

RTM_CON_EN_L |

|

Zone 3 Signal Descriptions

This topic provides descriptions of the signals listed in the following Zone 3

pin topics:

Table 3 Zone 3 Signal Descriptions

|

|

|---|

IPMI_SCL_L |

IPMI bus clock signal, as defined in AMC.0 specification. ARTM has a

pull-up resistor for this signal as indicated in AMC.0 specification. |

IPMI_SDA_L |

IPMI bus data signal,

as defined in AMC.0 specification. ARTM has a pull-up resistor for this signal

as indicated in AMC.0 specification. |

PS0#, PS1# |

Active low ARTM present signal. The PS0# is linked

to logic GND on the ATCA blade, PS1# is pulled up to

3.3V Management Power on the ATCA blade, PS0# and PS1# is connected through diode

on ARTM, exactly as defined in AMC.0 specification. PS1# is last mate on

Power connector and PS0# is on the opposite end of the set of

connectors. Logic low on PS1# indicates that ARTM is present and fully inserted. |

Enable# |

When

low, indicates to ARTM that it is fully inserted and that MMC can

start execution. Logic high keeps MMC in reset state. This signal has a

pull-up resistor as indicated in AMC.0 specification. |

Shelf_GND |

Frame/Chassis Safety Ground. |

Logic_GND |

(Logic 0vdc). Logic Ground-Common return for

Management Power Payload Power, reference potential for single-ended logic signaling, and shielding for

differential pair signals in the AMC connector. |

12VPP |

12V Payload Power, enabled after successful E-keying, following

AMC.0 specification. ARTM meets requirements posted for payload power in AMC specification. |

3.3V_MP |

3.3V Management

Power. ARTM meets requirements posted for management power in AMC.0 specification. |

RX |

AMC Extended Options

receive differential pair signals. Note that this specification takes ATCA blade perspective, which means

that RX signals are driven by ARTM and received by ATCA blade. |

TX |

AMC Extended

Options transmit differential pair signals. Note that this specification takes ATCA blade perspective, which

means that TX signals are driven by ATCA blade and received by ARTM. |

SA_TX |

SAS

or SATA transmit differential pair signals. |

SA_RX |

SAS or SATA receive differential pair signals. |

Serial 0 |

RS-232 Serial

Signals, Transmit, Receive, Clear to Send, Request to Send, Data Terminal Ready, and

Data Set Ready. |

LAN0 |

10/100/1000BASE-T signals. |

LAN0_CTV |

10/100/1000BASE-T transformer Center Tap signal, which could be used to terminate

center tap of transformers placed on the ARTM. This signal is applicable if

Ethernet PHY is located on ATCA blade, while transformers are located on ARTM. |

ACT_LED# |

LAN

0 (Management) activity indicator signal for LED (active low). |

LINK_LED# |

LAN 0 (Management) LINK indicator

signal for LED (active low). |

PCI_CFG |

PCI Express bus configuration signal. It must be grounded on

ARTMs that use a single x8 PCI Express bus and pulled up on

the ATCA with 10Kohm resistor to management power. On ARTMs that expect two

x4 PCI-Express buses, this pin will float (not be connected). Two x4 PCI-Express

buses are intended for ARTM implementations that desire to avoid PCI-Express switch in

order to reduce latency. |

ARTM# |

ARTM# signal must be grounded on ARTMs that implement MMC controller

as defined by AMC.0 specification. This signal is pulled up with 10Kohm resistor

to management power on the ATCA node blade server. |

SLAN_TX |

GBEthernet SerDes transmit differential pair signals. |

SLAN_RX |

GBEthernet

SerDes receive differential pair signals. |

PETx |

PCI-Express transmit differential pair signals. |

PERx |

PCI-Express receive differential pair signals. |

PCI_RST# |

PCI-Express reset signal.

Logic low resets downstream PCI-Express devices on ARTM. |

TCLKA |

PCI-Telecom clock A 19.44 MHz, differential pair

into ARTM (ATCA CLK2) as defined in AMC.0 specification. |

TCLKB |

PCI-Telecom clock B 19.44

MHz, differential pair out from ARTM (ATCA CLK3) as defined in AMC.0 specification. |

TCLKC |

PCI-Telecom

clock C 8 kHz, differential pair into ARTM (ATCA CLK1) as defined in

AMC.0 specification. |

TCLKD |

PCI-Telecom clock D 8 kHz, differential pair out from ARTM as defined

in AMC.0 specification. |

FCLKA |

Fabric clock, as defined in AMC.0 specification. Intended to be used

for PCI-Express 100 MHz spread spectrum clock. |

TCK, TMS, TRST#, TDO, TDI |

JTAG signals.

Signal direction follows AMC.0 specification. |

|