2.2.3 倍精度形式

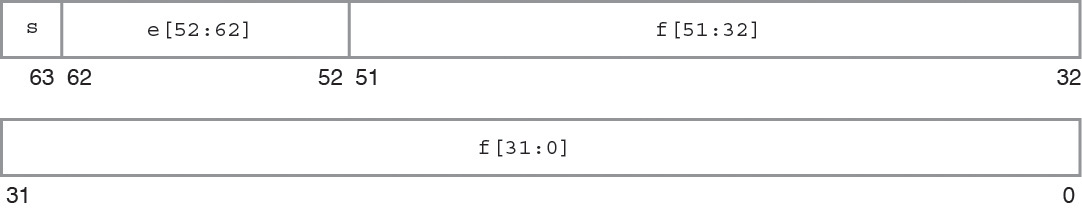

IEEE 倍精度形式は、52 ビットの小数部 f、11 ビットのバイアス付き指数 e、および 1 ビットの符号 s の 3 つのフィールドで構成されています。 これらのフィールドは、次の図に示すように、アドレスが連続した 2 つの 32 ビットワードに連続して格納されます。

SPARC アーキテクチャーでは、上位アドレスの 32 ビットワードに小数部の最下位 32 ビットが含まれるのに対して、x86 アーキテクチャーでは、下位アドレスの 32 ビットワードに小数部の最下位 32 ビットが含まれます。

f[31:0] が小数部の最下位 32 ビットを示している場合は、ビット 0 が小数部全体の最下位ビットであり、ビット 31 は小数部の最下位 32 ビットの最上位ビットです。

もう一方の 32 ビットワードでは、ビット 0:19 には小数部の最上位 20 ビット f[51:32] が含まれ (ビット 0 がこれらの小数部の最上位 20 ビットの最下位ビット、ビット 19 が小数部全体の最上位ビット)、ビット 20:30 には 11 ビットのバイアス付き指数 e が含まれ (ビット 20 がバイアス付き指数の最下位ビット、ビット 30 が最上位ビット)、最上位ビット 31 には符号ビット s が含まれています。

次の図では、2 つの連続した 32 ビットワードが 1 つの 64 ビットワードであるかのように各ビットに番号を付けています。そこでは、ビット 0:51 に 52 ビットの小数部 f が格納され、ビット 52:62 に 11 ビットのバイアス付き指数 e が格納され、ビット 63 に符号ビット s が格納されています。

図 2-2 倍精度格納形式

これらの 3 つのフィールド内のビットパターンの値によって、ビットパターン全体で表される値が決定されます。

Table 2–4 は、一方にある 3 つの構成フィールド内のビットの値と、もう一方にある倍精度形式のビットパターンによって表される値の間の対応関係を示しています。u は、示されているフィールドの値が、倍精度形式の特定のビットパターンの値の決定には関係しないことを示しています。

|

e < 2047 の場合、倍精度形式のビットパターンに割り当てられる値は、小数部の最上位ビットのすぐ左側に 2 進基数点を挿入し、2 進小数点のすぐ左側に暗黙ビットを挿入することによって形成されます。このように形成された数値は、仮数と呼ばれます。暗黙ビットにこの名前が付けられているのは、その値が倍精度形式のビットパターンでは明示的に指定されておらず、バイアス付き指数フィールドの値によって暗に示されているためです。

倍精度形式の場合、正規数と非正規数の違いは、正規数の仮数の先行ビット (2 進小数点の左側のビット) が 1 であるのに対して、非正規数の仮数の先行ビットは 0 である点です。 倍精度形式の非正規数は、IEEE 規格 754 では倍精度形式の非正規化数という名前になりました。

52 ビットの小数部が暗黙的先行仮数ビットと組み合わされて、倍精度形式の正規数の 53 ビットの精度が実現されます。

倍精度格納形式での重要なビットパターンの例をTable 2–5 に示します。 2 番目の列のビットパターンは、2 つの 8 桁 16 進数として示されています。SPARC アーキテクチャーでは、左側が下位アドレスの 32 ビットワードの値であり、右側が上位アドレスの 32 ビットワードの値であるのに対して、x86 アーキテクチャーでは、左側は上位アドレスのワードであり、右側は下位アドレスのワードです。最大の正の正規数は、IEEE 倍精度形式で表すことができる最大の有限数です。最小の正の非正規数は、IEEE 倍精度形式で表すことができる最小の正の数値です。最小の正の正規数は多くの場合、アンダーフローしきい値と呼ばれます。(最大と最小の正規数および非正規数に対する 10 進数値は近似値であり、示されている桁数に関して正確です。)

|

NaN (非数) は、NaN の定義を満足させる多くのビットパターンのいずれかで表すことができます。Table 2–5 に示されている NaN の 16 進数値は、NaN を表すために使用できる多くのビットパターンの 1 つにすぎません。