2.2.5 拡張倍精度形式 (x86)

この浮動小数点環境の拡張倍精度形式は、拡張倍精度形式の IEEE 定義に準拠しています。 これは、63 ビットの小数部 f、1 ビットの明示的先行仮数ビット j、15 ビットのバイアス付き指数 e、および 1 ビットの符号 s の 4 つのフィールドで構成されています。 この形式は、SPARC 用の Oracle Solaris Studio Fortran または C/C++ の言語の型としては使用できません。

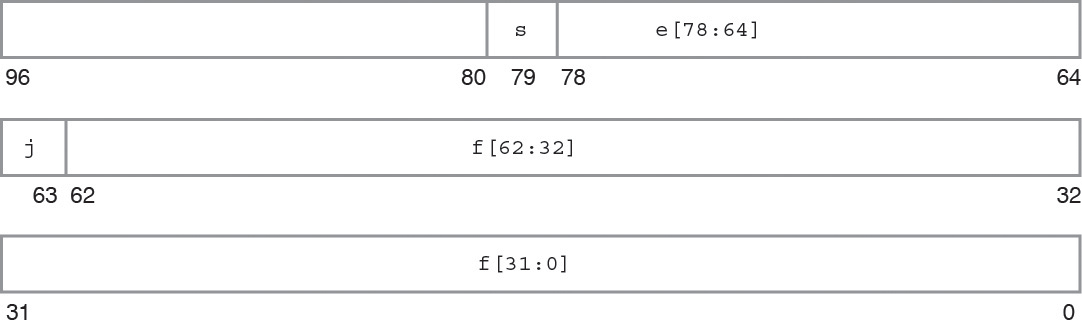

x86 アーキテクチャーファミリでは、これらのフィールドは、アドレスが連続した 10 個の 8 ビットバイトに連続して格納されます。ただし、UNIX System V Application Binary Interface Intel 386 Processor Supplement (Intel ABI) では、次の図に示すように、拡張倍精度のパラメータや結果がスタック内でアドレスが連続した 3 つの 32 ビットワード (最上位アドレスのワードの最上位 16 ビットは未使用) を占有する必要があります。

最下位アドレスの 32 ビットワードには、小数部 f[31:0] の最下位 32 ビットが含まれています (ビット 0 が小数部全体の最下位ビット、ビット 31 が小数部の最下位 32 ビットの最上位ビット)。中央のアドレスの 32 ビットワードでは、ビット 0:30 には小数部の最上位 31 ビット f[62:32] が含まれ (ビット 0 がこれらの小数部の最上位 31 ビットの最下位ビット、ビット 30 が小数部全体の最上位ビット)、この中央のアドレスの 32 ビットワードのビット 31 には明示的先行仮数ビット j が含まれています。

最上位アドレスの 32 ビットワードでは、ビット 0:14 には 15 ビットのバイアス付き指数 e が含まれ (ビット 0 がバイアス付き指数の最下位ビット、ビット 14 が最上位ビット)、ビット 15 には符号ビット s が含まれています。 この最上位アドレスの 32 ビットワードの最上位 16 ビットは x86 アーキテクチャーファミリでは未使用ですが、上で示したように、それらの存在は Intel ABI への準拠のために不可欠です。

次の図では、3 つの連続した 32 ビットワードが 1 つの 96 ビットワードであるかのように各ビットに番号を付けています。そこでは、ビット 0:62 に 63 ビットの小数部 f が格納され、ビット 63 に明示的先行仮数ビット j が格納され、ビット 64:78 に 15 ビットのバイアス付き指数 e が格納され、ビット 79 に符号ビット s が格納されています。

図 2-4 拡張倍精度形式 (x86)

4 つのフィールド f、j、e、および s 内のビットパターンの値によって、ビットパターン全体で表される値が決定されます。

Table 2–8 は、4 つの構成フィールドの 16 進数表現と、各ビットパターンによって表される値の間の対応関係を示しています。u は、示されているフィールドの値が特定のビットパターンの値の決定には関係しないことを示しています。

|

拡張倍精度形式のビットパターンには暗黙的先行仮数ビットが含まれていないことに注意してください。拡張倍精度形式では、先行仮数ビットは個別のフィールド j として明示的に指定されます。ただし、e ≠ 0 の場合、j = 0 を含むビットパターンはすべて、このようなビットパターンを浮動小数点演算のオペランドとして使用すると無効な演算の例外が発生するという意味でサポートされていません。

拡張倍精度形式内の互いに素なフィールド j と f の和集合は、仮数と呼ばれます。e < 32767 かつ j = 1 の場合、または e = 0 かつ j = 0 の場合、この仮数は、先行仮数ビット j と小数部の最上位ビットの間に 2 進基数点を挿入することによって形成されます。

x86 拡張倍精度形式では、先行仮数ビット j が 0 で、かつバイアス付き指数フィールド e も 0 であるビットパターンが非正規数を表すのに対して、先行仮数ビット j が 1 で、かつバイアス付き指数フィールド e が 0 以外であるビットパターンは正規数を表します。先行仮数ビットは指数の値から推測されるのではなく、明示的に表されるため、この形式では (非正規数のように) バイアス付き指数は 0 だが、先行仮数ビットが 1 であるビットパターンも認められます。このような各ビットパターンは、実際にはバイアス付き指数フィールドが 1 である対応するビットパターン (つまり、正規数) と同じ値を表すため、これらのビットパターンは擬似非正規数と呼ばれます。非正規数は、IEEE 規格 754-1985 では非正規化数という名前になりました。擬似非正規数は単に、x86 拡張倍精度形式のエンコーディングのアーティファクトです。オペランドとして現れると対応する正規数に暗黙的に変換され、結果として生成されることはありません。

|

拡張倍精度格納形式の重要なビットパターンの例が前の表に示されています。2 番目の列のビットパターンは、1 つの 4 桁 16 進数と、それに続く 2 つの 8 桁 16 進数として示されています。前者は、最上位アドレスの 32 ビットワードの最下位 16 ビットの値です (この最上位アドレスの 32 ビットワードの最上位 16 ビットは未使用であるため、それらの値は示されていません)。後者は、左側が中央のアドレスの 32 ビットワードの値であり、右側が最下位アドレスの 32 ビットワードの値です。最大の正の正規数は、x86 拡張倍精度形式で表すことができる最大の有限数です。最小の正の非正規数は、拡張倍精度形式で表すことができる最小の正の数値です。最小の正の正規数は多くの場合、アンダーフローしきい値と呼ばれます。最大と最小の正規数および非正規数に対する 10 進数値は近似値であり、示されている桁数に関して正確です。

NaN (非数) は、NaN の定義を満足させる多くのビットパターンのいずれかで表すことができます。前の表に示されている NaN の 16 進数値は、小数部フィールドの先行 (最上位) ビットによって、NaN がシグナルを発生しない NaN (先行小数ビット = 1) またはシグナルを発生する NaN (先行小数ビット = 0) のどちらであるかが決定されることを示しています。