Architecture d'E/S physique

L'architecture d'E/S physique pour ces serveurs a changé depuis les versions précédentes des serveurs de série M. Des noms différents sont utilisés et la CPU ne détient plus la topologie Fabric de PCIe.

Terminologie relative aux E/S

Voici les modifications apportées aux termes utilisés pour décrire l'architecture d'E/S :

-

Complexe root - Dans un chemin de périphérique PCIe, le complexe root est toujours le premier élément (par exemple, /pci@300). Dans les précédentes versions des serveurs de série M, les processeurs CMT contenaient un ou plusieurs complexes root. Cette fonctionnalité a été déplacée vers la puce de contrôleur d'E/S (IOH). Chaque serveur comporte une ou plusieurs puces de contrôleur d'E/S (IOH).

-

Port root - Un complexe root peut avoir un ou plusieurs ports root. Les ports root sont indépendants les uns des autres dans cette topologie Fabric. Toutefois, tout périphérique figurant sous le même complexe root partage cette topologie Fabric.

Le port root est toujours le deuxième terme dans le chemin d'un périphérique PCIe. Le premier port root sera toujours pci@1, le deuxième sera pci@2, etc.

-

Bus PCI - Il s'agit du libellé que vous utilisez pour affecter un complexe root à un domaine logique.

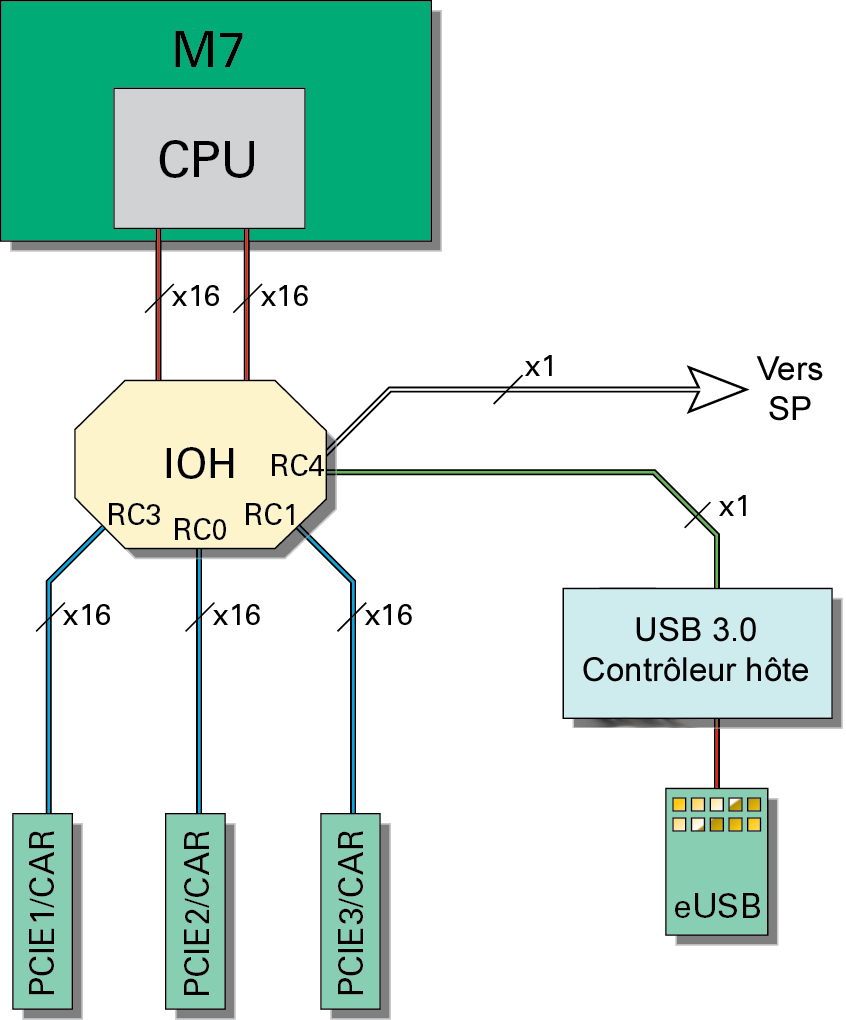

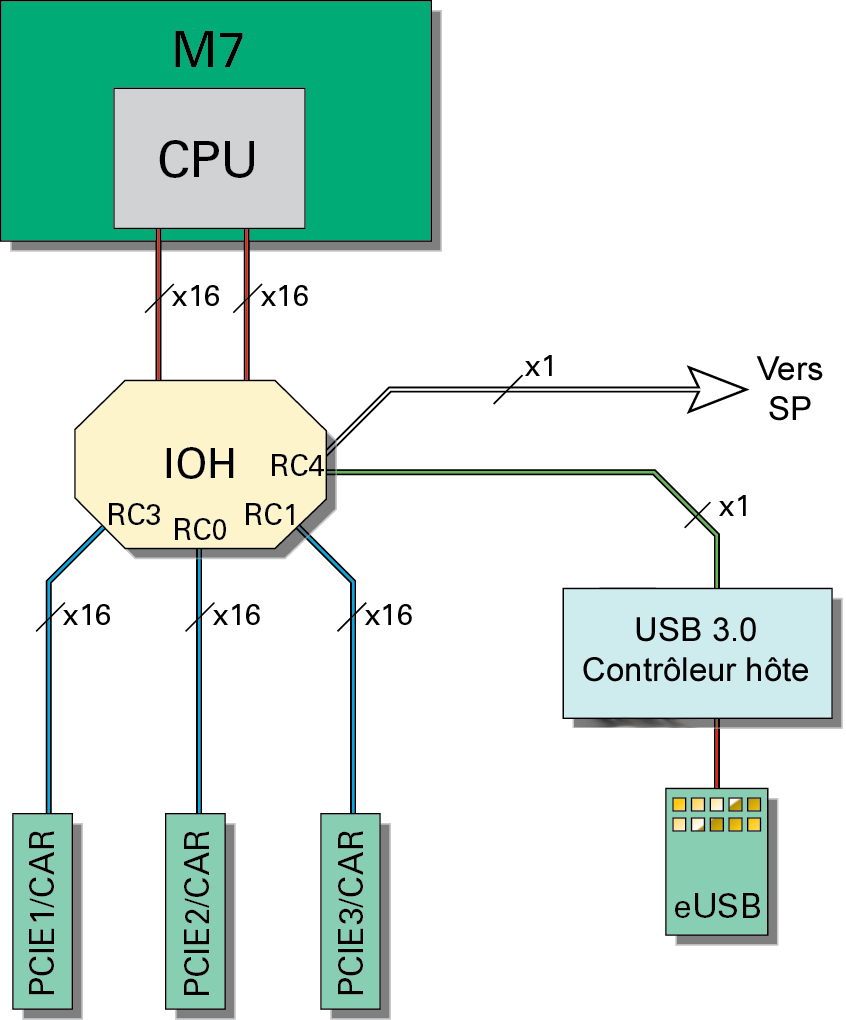

Affectations de complexe root

La figure ci-après présente les affectations de complexe root pour une CMIOU.

Chaque complexe root a un chemin de périphérique, un chemin de service et un nom de bus. Ce tableau contient la dénomination pour les CMIOU0 et CMIOU1 à titre d'exemples. Pour tous les exemples de dénomination des CMIOU, reportez-vous à la section Architecture d'E/S physique.

|

|

|

|

|

|

CMIOU0

|

/pci@301/pci@1

|

/SYS/CMIOU0/PCIE3

|

pci_1

|

Généralement utilisé pour l'adaptateur de disque d'initialisation.

|

|

/pci@300/pci@1

|

/SYS/CMIOU0/PCIE2

|

pci_0

|

|

|

/pci@303/pci@1

|

/SYS/CMIOU0/PCIE1

|

pci_3

|

|

|

CMIOU1

|

/pci@306/pci@1

|

/SYS/CMIOU1/PCIE3

|

pci_6

|

Généralement utilisé pour l'adaptateur réseau.

|

|

/pci@305/pci@1

|

/SYS/CMIOU1/PCIE2

|

pci_5

|

|

|

/pci@308/pci@1

|

/SYS/CMIOU1/PCIE1

|

pci_8

|

|

|

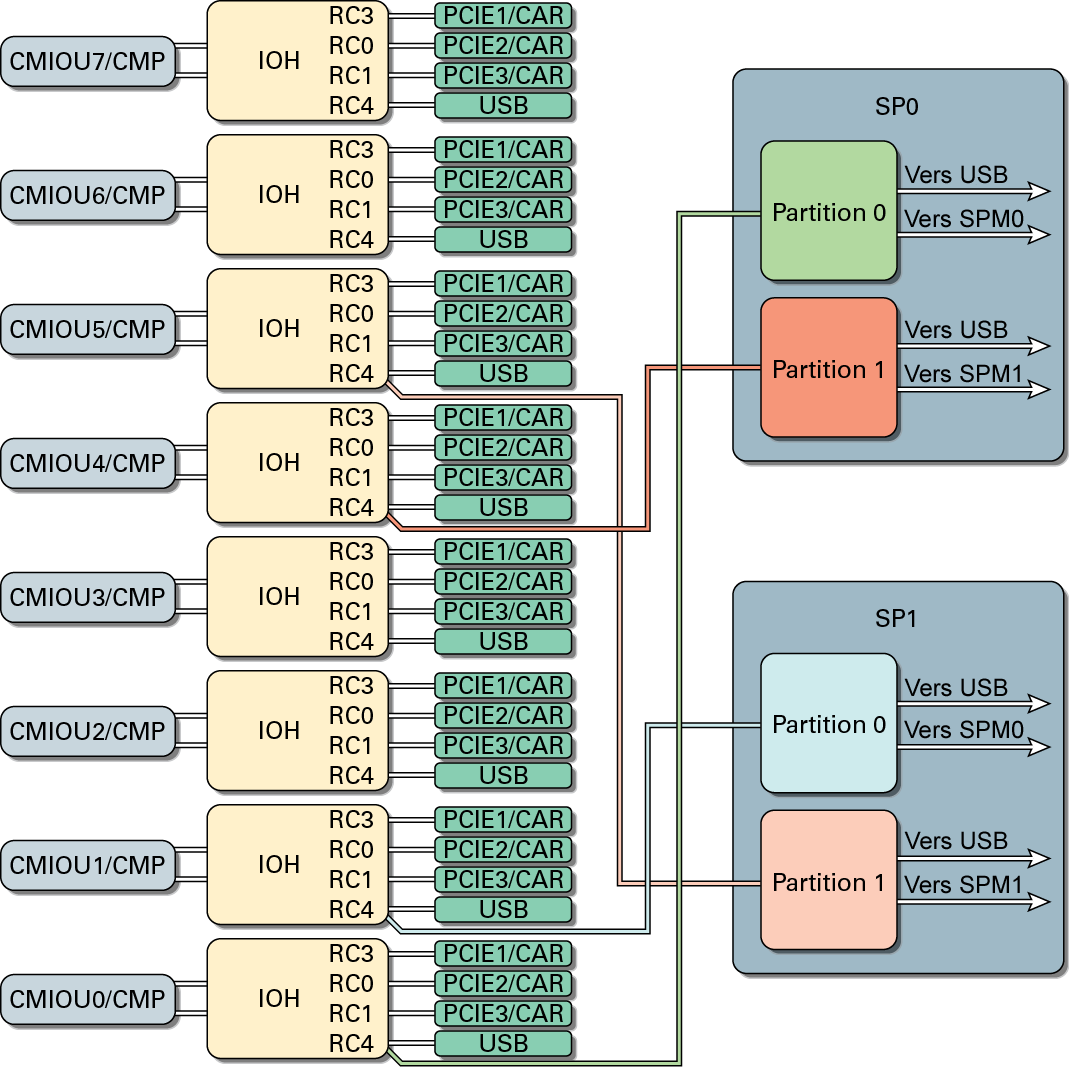

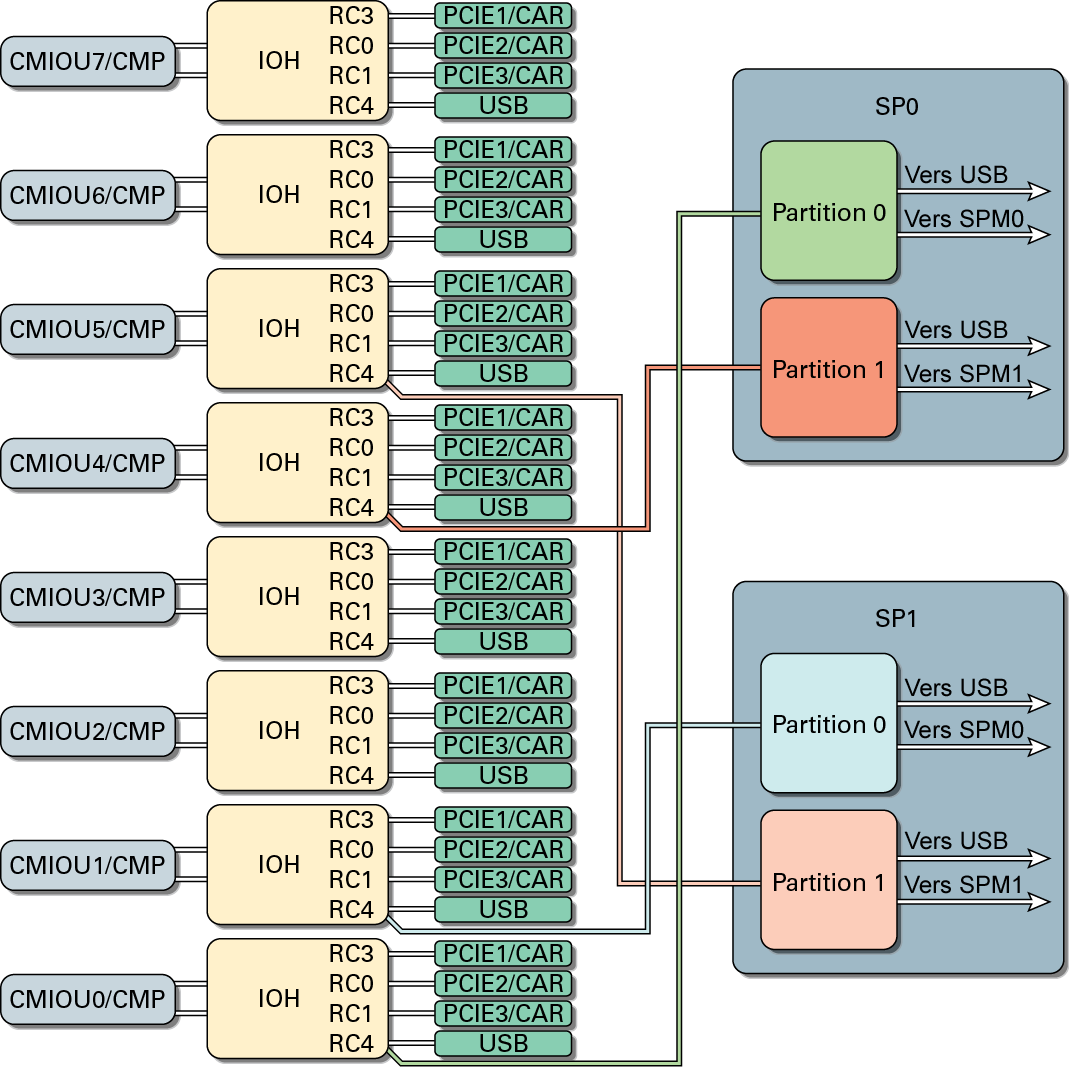

Disposition de l'architecture d'E/S

Le diagramme suivant présente la disposition de l'architecture d'E/S pour le serveur SPARC M7-8 avec un domaine physique. Pour le serveur SPARC M7-16, le diagramme représente une moitié de l'architecture d'E/S. Pour le serveur SPARC M7-8 avec deux domaines physiques, le diagramme représente la disposition de l'architecture d'E/S pour les deux domaines statiques.

Remarque -

Le diagramme suivant présente les connexions entre les SP et les CMIOU4 et CMIOU5. Bien que les broches soient présentes, les connexions ne sont pas actives dans le serveur SPARC M7-8 avec un domaine physique. Elles sont actives dans le serveur SPARC M7-8 comportant deux domaines physiques et dans les serveurs SPARC M7-16.

Exemple de sortie des composants d'E/S

La commande ldm list-io affiche les informations sur les périphériques d'E/S du serveur. En examinant la sortie de la commande ldm list-io, vous pouvez déterminer le complexe root et le port root d'un périphérique PCIe installé (indiqué entre crochets dans la sortie), le numéro de l'emplacement (par exemple, PCIE2 est l'emplacement 2 sur la CMIOU0), et à des fins d'administration, le nom du BUS (par exemple, pci_0) que vous utilisez pour affecter un complexe root à un domaine logique Cette sortie a été modifiée pour plus de clarté.

# ldm list-io -l

NAME TYPE BUS DOMAIN STATUS

---- ---- --- ------ ------

...

/SYS/CMIOU0/PCIE2 PCIE pci_0 primary EMP

[pci@300/pci@1]

/SYS/CMIOU0/PCIE3 PCIE pci_1 primary OCC

[pci@301/pci@1]

LSI,sas@0/iport@80

LSI,sas@0/iport@v0

/SYS/CMIOU0/PCIE1 PCIE pci_3 primary OCC

[pci@303/pci@1]

network@0

network@0,1

network@0,2

network@0,3

...

#

Relations entre les composants d'E/S

Les tableaux suivants présentent les relations entre les numéros du complexe root, les numéros des emplacements PCIe, les noms du complexe root et les noms des bus sur chaque CMIOU que vous pouvez installer dans les serveurs.

Ce tableau explique les composants DCU et CMIOU des serveurs.

|

|

|

|

SPARC M7-8 (deux domaines physiques)

|

Deux statiques avec quatre unités CMIOU chacune

|

|

|

SPARC M7-8 (un domaine physique)

|

Une statique avec huit unités CMIOU

|

CMIOU0–7

|

|

SPARC M7-16

|

Quatre dynamiques avec quatre unités CMIOU chacune

|

-

CMIOU0–3

-

CMIOU4–7

-

CMIOU8–11

-

CMIOU12–15

|

|

Table 1 Dénomination des composants d'E/S pour la CMIOU0

|

|

|

|

|

0

|

PCIE2

|

pci@300

|

pci_0

|

|

1

|

PCIE3

|

pci@301

|

pci_1

|

|

3

|

PCIE1

|

pci@303

|

pci_3

|

|

4

|

N/A

|

pci@304

|

pci_4

|

|

Table 2 Dénomination des composants d'E/S pour la CMIOU1

|

|

|

|

|

0

|

PCIe2

|

pci@305

|

pci_5

|

|

1

|

PCIE3

|

pci@306

|

pci_6

|

|

3

|

PCIE1

|

pci@308

|

pci_8

|

|

4

|

N/A

|

pci@309

|

pci_9

|

|

Table 3 Dénomination des composants d'E/S pour la CMIOU2

|

|

|

|

|

0

|

PCIE2

|

pci@30a

|

pci_10

|

|

1

|

PCIE3

|

pci@30b

|

pci_11

|

|

3

|

PCIE1

|

pci@30d

|

pci_13

|

|

4

|

N/A

|

pci@30e

|

pci_14

|

|

Table 4 Dénomination des composants d'E/S pour la CMIOU3

|

|

|

|

|

0

|

PCIE2

|

pci@30f

|

pci_15

|

|

1

|

PCIE3

|

pci@310

|

pci_16

|

|

3

|

PCIE1

|

pci@312

|

pci_18

|

|

4

|

N/A

|

pci@313

|

pci_19

|

|

Table 5 Dénomination des composants d'E/S pour la CMIOU4

|

|

|

|

|

0

|

PCIE2

|

pci@314

|

pci_20

|

|

1

|

PCIE3

|

pci@315

|

pci_21

|

|

3

|

PCIE1

|

pci@317

|

pci_23

|

|

4

|

N/A

|

pci@318

|

pci_24

|

|

Table 6 Dénomination des composants d'E/S pour la CMIOU5

|

|

|

|

|

0

|

PCIE2

|

pci@319

|

pci_25

|

|

1

|

PCIE3

|

pci@31a

|

pci_26

|

|

3

|

PCIE1

|

pci@31c

|

pci_28

|

|

4

|

N/A

|

pci@31d

|

pci_29

|

|

Table 7 Dénomination des composants d'E/S pour la CMIOU6

|

|

|

|

|

0

|

PCIE2

|

pci@31e

|

pci_30

|

|

1

|

PCIE3

|

pci@31f

|

pci_31

|

|

3

|

PCIE1

|

pci@321

|

pci_33

|

|

4

|

N/A

|

pci@322

|

pci_34

|

|

Table 8 Dénomination des composants d'E/S pour la CMIOU7

|

|

|

|

|

0

|

PCIE2

|

pci@323

|

pci_35

|

|

1

|

PCIE3

|

pci@324

|

pci_36

|

|

3

|

PCIE1

|

pci@326

|

pci_38

|

|

4

|

N/A

|

pci@327

|

pci_39

|

|

Table 9 Dénomination des composants d'E/S pour la CMIOU8

|

|

|

|

|

0

|

PCIE2

|

pci@328

|

pci_40

|

|

1

|

PCIE3

|

pci@329

|

pci_41

|

|

3

|

PCIE1

|

pci@32b

|

pci_43

|

|

4

|

N/A

|

pci@32c

|

pci_44

|

|

Table 10 Dénomination des composants d'E/S pour la CMIOU9

|

|

|

|

|

0

|

PCIE2

|

pci@32d

|

pci_45

|

|

1

|

PCIE3

|

pci@32e

|

pci_46

|

|

3

|

PCIE1

|

pci@330

|

pci_48

|

|

4

|

N/A

|

pci@331

|

pci_49

|

|

Table 11 Dénomination des composants d'E/S pour la CMIOU10

|

|

|

|

|

0

|

PCIE2

|

pci@332

|

pci_50

|

|

1

|

PCIE3

|

pci@333

|

pci_51

|

|

3

|

PCIE1

|

pci@335

|

pci_53

|

|

4

|

N/A

|

pci@336

|

pci_54

|

|

Table 12 Dénomination des composants d'E/S pour la CMIOU11

|

|

|

|

|

0

|

PCIE2

|

pci@337

|

pci_55

|

|

1

|

PCIE3

|

pci@338

|

pci_56

|

|

3

|

PCIE1

|

pci@33a

|

pci_58

|

|

4

|

N/A

|

pci@33b

|

pci_59

|

|

Table 13 Dénomination des composants d'E/S pour la CMIOU12

|

|

|

|

|

0

|

PCIE2

|

pci@33c

|

pci_60

|

|

1

|

PCIE3

|

pci@33d

|

pci_61

|

|

3

|

PCIE1

|

pci@33f

|

pci_63

|

|

4

|

N/A

|

pci@340

|

pci_64

|

|

Table 14 Dénomination des composants d'E/S pour la CMIOU13

|

|

|

|

|

0

|

PCIE2

|

pci@341

|

pci_65

|

|

1

|

PCIE3

|

pci@342

|

pci_66

|

|

3

|

PCIE1

|

pci@344

|

pci_68

|

|

4

|

N/A

|

pci@345

|

pci_69

|

|

Table 15 Dénomination des composants d'E/S pour la CMIOU14

|

|

|

|

|

0

|

PCIE2

|

pci@346

|

pci_70

|

|

1

|

PCIE3

|

pci@347

|

pci_71

|

|

3

|

PCIE1

|

pci@349

|

pci_73

|

|

4

|

N/A

|

pci@34a

|

pci_74

|

|

Table 16 Dénomination des composants d'E/S pour la CMIOU15

|

|

|

|

|

0

|

PCIE2

|

pci@34b

|

pci_75

|

|

1

|

PCIE3

|

pci@34c

|

pci_76

|

|

3

|

PCIE1

|

pci@34e

|

pci_78

|

|

4

|

N/A

|

pci@34f

|

pci_79

|

|