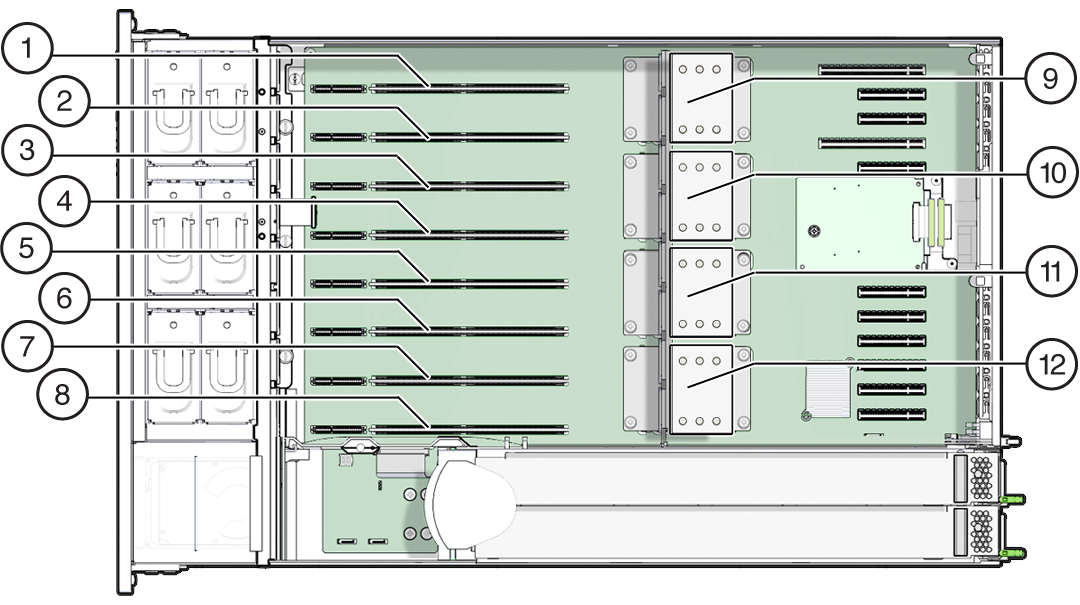

CPU y placa de memoria del controlador ZS5-4

Los cuatro sockets de la CPU están ubicados en el medio del controlador y se designan de manera consecutiva de derecha a izquierda (desde la parte frontal del controlador). El socket del extremo derecho es CPU-0 y se designa como P0, y el socket del extremo izquierdo es CPU-3 y se designa como P3.

Las ocho ranuras de placa de memoria (MR) se ubican entre las ranuras del módulo de ventiladores y los sockets de la CPU. De manera consecutiva de derecha a izquierda, la ranura del extremo derecho es la ranura 0 y la ranura del extremo izquierdo es la ranura 7.

Las ranuras también están designadas por su asociación con los cuatro sockets de la CPU (P0-P3). Se asignan dos ranuras a cada socket de la CPU. Por ejemplo, las ranuras 0 y 1 se asocian con el socket de la CPU P0, y se designan como P0/MR0 y P0/MR1. Las ranuras 2 y 3 se asocian con el socket de la CPU P1, y se designan como P1/MR0 y P1/MR1. Este patrón de numeración continúa para las ranuras restantes.

|

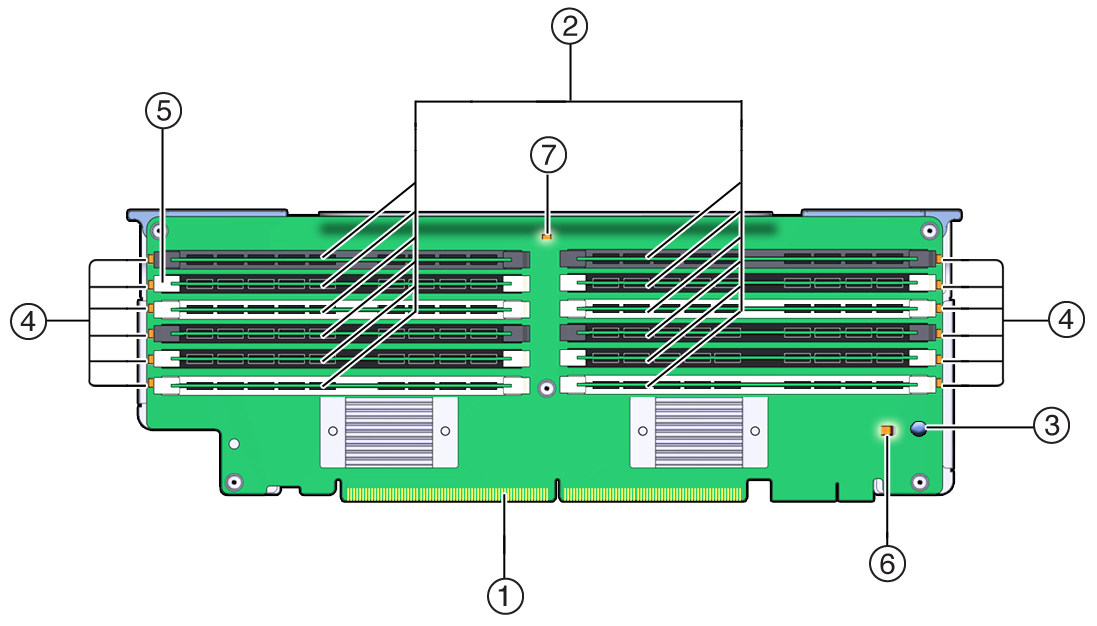

Componentes de la placa de memoria

En la siguiente ilustración, se muestran los componentes de la placa de memoria.

|

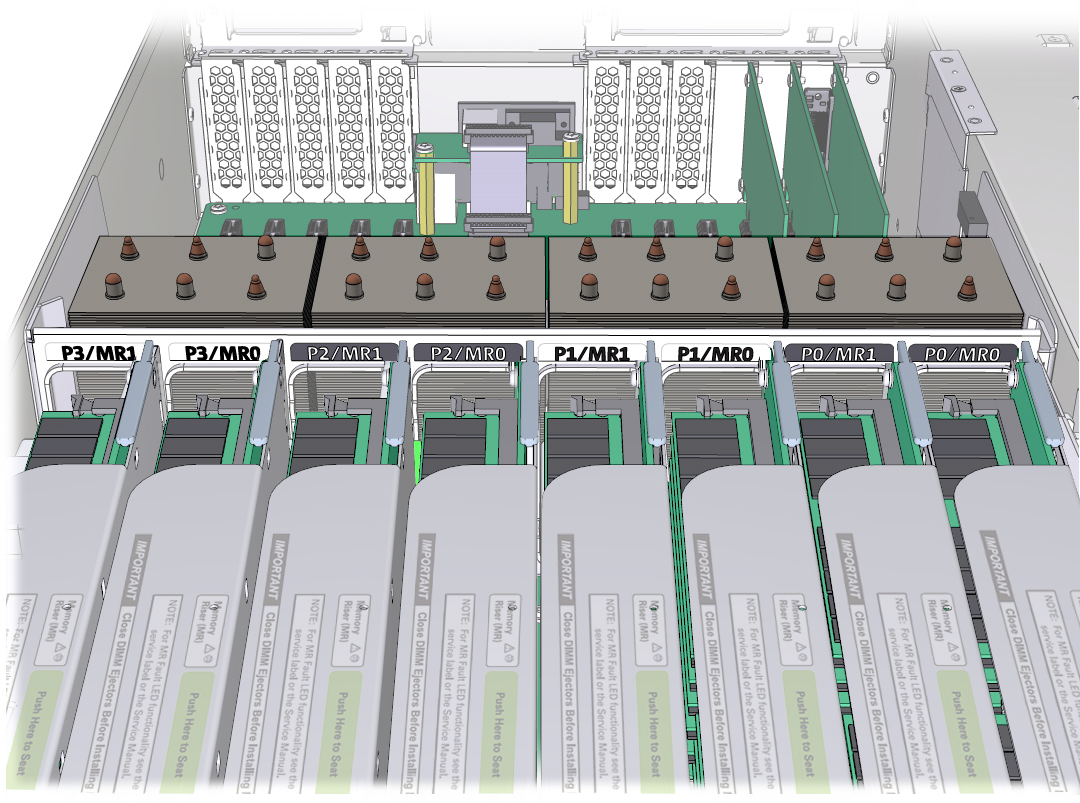

Diseño físico de las placas de memoria

Las placas de memoria se ubican en la parte trasera del compartimiento del módulo de ventiladores. Las designaciones de cada placa de memoria (MR) y sus CPU asociadas se ubican dentro del controlador con etiquetas fijadas en el soporte posterior de la placa de memoria. Las placas se designan como MR, y las CPU se designan como P. Las ranuras y las CPU se etiquetan de derecha a izquierda si se las mira desde la parte frontal del controlador como se muestra a continuación:

Notas - Cada CPU tiene dos ranuras de placa asignadas (MR0 y MR1).

P0/MR0 (ranura del extremo derecho)

P0/MR1

P1/MR0

P1/MR1

P2/MR0

P2/MR1

P3/MR0

P3/MR1 (ranura del extremo izquierdo)

En la siguiente ilustración, se muestra la numeración de las ranuras de la placa de memoria y las CPU asociadas como se describió anteriormente:

Reglas de asignación de placas de memoria

Las reglas de asignación de las placas de memoria del controlador son las siguientes:

Cada CPU tiene dos ranuras de placa de memoria dedicadas (MR0 y MR1).

Las ranuras de las placas de memoria dedicadas para cada CPU instalada deben contener una placa de memoria. Un sistema con cuatro CPU debe contener ocho placas de memoria.

Cuando asigne placas de memoria al controlador:

Primero asigne la ranura de la placa MR0 para cada CPU, comenzando por la que tiene el número más bajo de CPU (P0).

Luego asigne la ranura de la placa MR1 para cada CPU, comenzando por la que tiene el número más bajo de CPU (P0).